| Title        | アプリケーションに適応した組込みプロセッサとリア<br>ルタイムOSの自動生成に関する研究 |  |  |

|--------------|-----------------------------------------------|--|--|

| Author(s)    | 宮内,哲夫                                         |  |  |

| Citation     |                                               |  |  |

| Issue Date   | 2021-03                                       |  |  |

| Туре         | Thesis or Dissertation                        |  |  |

| Text version | ETD                                           |  |  |

| URL          | http://hdl.handle.net/10119/17480             |  |  |

| Rights       |                                               |  |  |

| Description  | Supervisor:田中 清史,情報科学研究科,博士                   |  |  |

#### **Doctoral Dissertation**

# A Study on Automatic Generation of Embedded Processors and Real-Time OS Adapted to Applications

Tetsuo Miyauchi

Supervisor: Professor Kiyofumi Tanaka

School of Information Science Japan Advanced Institute of Science and Technology

March, 2021

#### Abstract

In recent years, the use of embedded microprocessors has been increasing with prevailing IoT (Internet of Things) and RTOSs are commonly used to develop a real-time system effectively. By using an RTOS, a complicated procedure can be divided into tasks with real-time scheduling based on the preemptive and priority-based task scheduling, and a real-time application can be developed easily with using RTOS functions such as task management, task dependent synchronization, synchronization and communication. While there are advantages for using an RTOS, an RTOS itself consumes additional memory, computational resources and power. Based on these points, our research objectives are as follows: (1) Build an application adaptive processor core. (2) Remove unused codes in RTOS kernel, while leaving necessary functions such as checking possible errors. (3) Implement hardware RTOS to reduce the amount of software resources and execution time. (4) Remove unused codes in a hardware RTOS as well as a software-only RTOS. (5) Build automatic development environment with which we can perform the items above.

In order to achieve the objectives, we adopted MIPS32 architecture for a processor core and illustrated the method for analyzing an application program and generating the application adaptive processor core circuit. In addition, we implemented two- to eight-core multi core processor on an FPGA and showed eight-core processor can be implemented on a relatively small FPGA with application adaptive processor cores.

Regarding RTOS, we proposed a framework to generate application adapted hardware RTOS and software-only RTOS. For the specification of an RTOS, we adopted  $\mu$ ITRON4.0 for the research as it is widely used and its specification is open in public. We propose the methods, "Removing Unnecessary Codes Caused by Fixed Attributes" and "Removing Unnecessary Codes Caused by the Way of Calling", for generating an application adaptive RTOS kernel. For the former method, as each system call is specified with attributes through parameters in a configuration file, functions which are not specified in the configuration file can be deleted from the RTOS kernel. For the latter method, error codes for system calls are defined in the RTOS specification whereas codes for checking errors which never occur in the application program remain in some cases. Since those codes are redundant when an application program is fixed, it is shown that how unnecessary error checking can be removed. In addition, we explained the structure of the hardware RTOS, which consists of RTOS Hardware Wrapper and RTOS Hardware Core. We propose an environment to generate an application adaptive processor core and a hardware/software-only RTOS kernel in a fully automatic manner.

For the evaluation of the effect of the proposal, we applied the proposed methods to several application programs and measured FPGA resources, RTOS kernel execution time and the size of the software parts. As a result, it can be seen that the hardware resources and the size of a software part of an RTOS kernel are reduced, and that the system call execution time is improved.

Keyword: processor, MIPS, RTOS,  $\mu$ ITRON, configuration, system call, FPGA, adaptation

#### Acknowledgments

I am most grateful to all people who have supported me to submit this dissertation, directly and indirectly. Especially, I would like to express my heartfelt gratitude to my supervisor, Professor Kiyofumi Tanaka of Japan Advanced Institute of Science and Technology (JAIST) for his patient guidance. My study began at the discussion with Professor Tanaka for my project paper's theme in my master course. Without his orientation, I could not complete the dissertation. I was always given useful comments in detail when I submitted papers until just before the deadline. Attending international conferences with him was also good experiences and I obtained lots of valuable advices for the presentation. I would also like to appreciate Professor Mineo Kaneko of JAIST, advisor for minor research project. He enlightened me as to suggestions for the dissertation especially for related work as well as my minor research project. I appreciate Professor Yasushi Inoguchi of JAIST, second supervisor, who gave me helpful comments, which increases the value of the dissertation. Furthermore, I appreciate Professor Yasuo Tan of JAIST and Professor Hironori Nakajo of Tokyo University of Agriculture and Technology for their comments on the dissertation. I learned a lot from their comments. In addition, I would like to thank all of professors in JAIST whose lectures I attended. All lectures without exception were very interesting and helpful for my background of continuous research. I also thank all members of Tanaka laboratory in Tokyo satellite and I feel it was precious experiences to have participated in a summer workshop and joint seminar with members in the Ishikawa campus. Their studies stimulated me to keep studying. Finally, I would like to express my appreciation for my family, who has encouraged me and supported my daily life.

# Contents

| 1        | $\mathbf{Intr}$ | oducti  | on                                                                 | 1  |

|----------|-----------------|---------|--------------------------------------------------------------------|----|

|          | 1.1             | Backg   | round                                                              | 1  |

|          | 1.2             | Contri  | bution                                                             | 7  |

|          | 1.3             | Struct  | ure of Dissertation                                                | 8  |

| <b>2</b> | Rela            | ated W  | Vork                                                               | 9  |

|          | 2.1             | Relate  | d Work                                                             | 9  |

|          |                 | 2.1.1   | Processor Core Adaptation                                          | 9  |

|          |                 | 2.1.2   | RTOS Kernel Adaptation                                             | 10 |

|          |                 | 2.1.3   | Software Overhead Mitigation                                       | 11 |

|          |                 | 2.1.4   | Hardware Scheduler                                                 | 11 |

|          |                 | 2.1.5   | Hardware RTOS                                                      | 11 |

|          |                 | 2.1.6   | Adaptation for Hardware RTOS Functions                             | 12 |

| 3        | Con             | struct  | ion of Automatic Development Environment for Adaptive Pro-         |    |

|          |                 | or Co   | re                                                                 | 14 |

|          | 3.1             | Struct  | ure of Processor Core                                              | 14 |

|          | 3.2             | Analy   | zing Application Program                                           | 18 |

|          |                 | 3.2.1   | Building Application Program                                       | 18 |

|          |                 | 3.2.2   | Analyzing Object Code                                              | 18 |

|          |                 | 3.2.3   | Extracting Instructions                                            | 18 |

|          |                 | 3.2.4   | Analyzing Object Code and Dependency Patterns                      | 19 |

|          | 3.3             | Selecti | ing Processor Resources with Used Instructions and Dependency Pat- |    |

|          |                 |         |                                                                    | 23 |

|          | 3.4             |         | ating Application Adaptive Processor Core Circuit                  | 24 |

|          | 3.5             | -       | imental Result                                                     | 25 |

|          |                 | 3.5.1   | Application Programs                                               | 25 |

|          |                 | 3.5.2   | Evaluation of Processor Adaptation                                 | 27 |

|          |                 | 3.5.3   | Discussion                                                         | 27 |

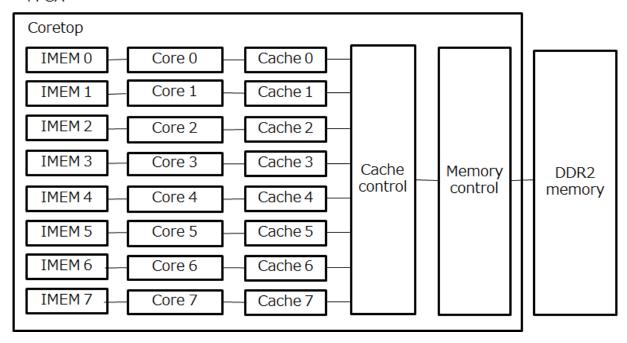

|          | 3.6             | Multio  |                                                                    | 28 |

|          |                 | 3.6.1   | Cache                                                              | 28 |

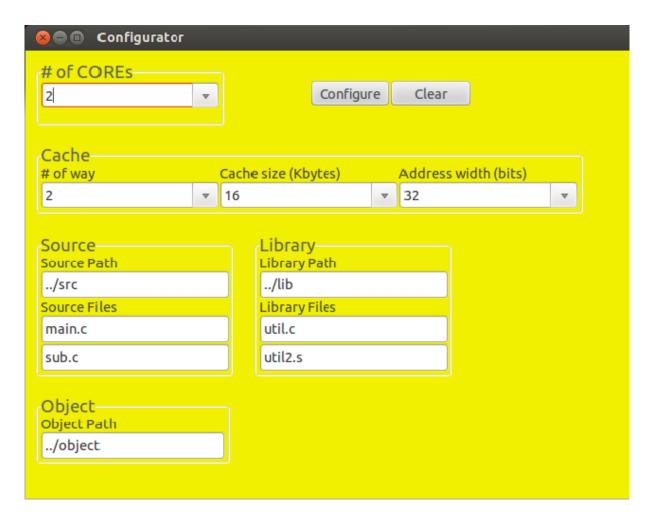

|          |                 | 3.6.2   | Multicore Configuration Environment                                | 29 |

|          |                 | 3.6.3   | Building Application Program                                       | 31 |

|          |                 | 3.6.4   | Analyzing Object Codes                                             | 31 |

|          |                 | 3.6.5   | Evaluation of Multi Core                                           | 31 |

|          | 27              | Summ    | ary of this Chapter                                                | 25 |

| 4            | Fran       | mework for Building Fine-Grained RTOS                         | 36         |

|--------------|------------|---------------------------------------------------------------|------------|

|              | 4.1        | Configuration Framework                                       | 36         |

|              | 4.2        | RTOS Structure                                                | 36         |

|              | 4.3        | Software Adaptation                                           | 37         |

|              |            | 4.3.1 Removing Unnecessary Codes Caused by Fixed Attributes   | 37         |

|              |            | 4.3.2 Removing Unnecessary Codes Caused by the Way of Calling |            |

|              | 4.4        | Hardware Adaptation                                           |            |

|              |            | 4.4.1 Structure of Hardware RTOS                              | 42         |

|              |            | 4.4.2 Interface to RTOS Hardware                              |            |

|              |            | 4.4.3 RTOS Hardware Wrapper                                   |            |

|              |            | 4.4.4 RTOS Hardware Core                                      | 49         |

|              | 4.5        | Development Process                                           | 52         |

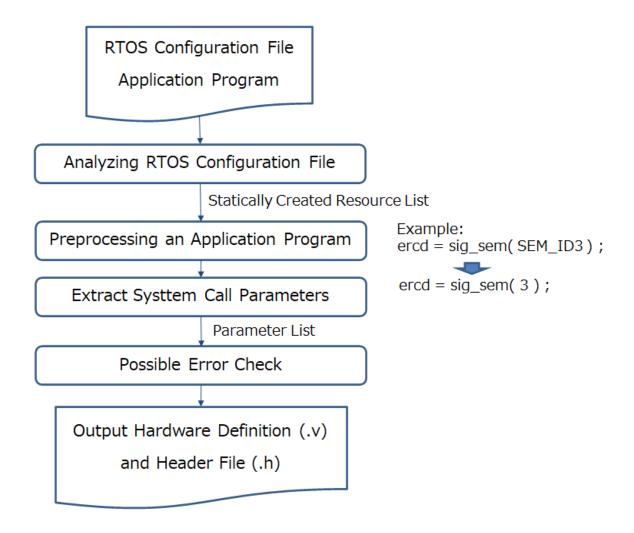

|              |            | 4.5.1 Parsing RTOS configuration file                         | 53         |

|              |            | 4.5.2 Analyzing Application Program                           | 53         |

|              |            | 4.5.3 Outputting Directives                                   | 54         |

|              |            | 4.5.4 Static Resource Creation                                |            |

|              |            | 4.5.5 RTOS Hardware Core                                      | 55         |

|              |            | 4.5.6 Generating Software Object File                         | 55         |

|              |            | 4.5.7 Generating Adaptive Processor Core                      | 55         |

|              |            | 4.5.8 Creating Software Program Object                        | 55         |

|              |            | 4.5.9 Implementation                                          | 55         |

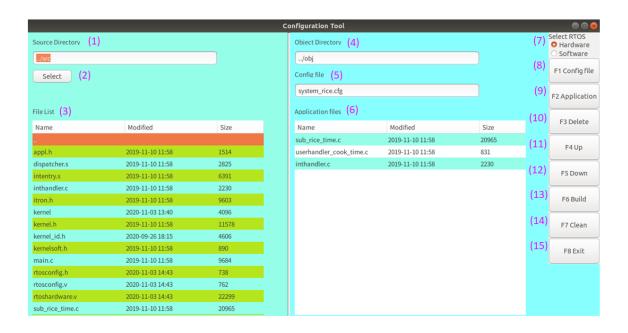

|              | 4.6        | GUI                                                           | 56         |

|              | 4.7        | Summary of this Chapter                                       | 57         |

| ۲            | E          | 14:                                                           | en         |

| 5            |            | luation                                                       | <b>62</b>  |

|              | 5.1<br>5.2 | Overview                                                      |            |

|              | _          | FPGA Resources                                                |            |

|              | 5.3        | Execution Time                                                |            |

|              | 5.4        | RTOS Kernel Size                                              |            |

|              | 5.5        | Discussion                                                    |            |

|              | 5.6        | Summary of this Chapter                                       | 69         |

| 6            | Con        | nclusion                                                      | <b>7</b> 5 |

|              | 6.1        | Summary of the Dissertation                                   | 75         |

|              | 6.2        | Conclusion                                                    |            |

|              | 6.3        | Future Work                                                   | 76         |

|              |            |                                                               |            |

| $\mathbf{A}$ |            | dix A                                                         | <b>7</b> 8 |

|              |            | INIT                                                          |            |

|              | A.2        | WAIT                                                          |            |

|              | A.3        | CHECK                                                         |            |

|              | A.4        | SETATTR                                                       |            |

|              | A.5        | TASKSTATUS                                                    |            |

|              | A.6        | SEMSTATUS                                                     |            |

|              | A.7        | FLGSTATUS                                                     |            |

|              | A.8        | DTQSTATUS                                                     |            |

|              | A.9        | CHECKTASK                                                     | 81         |

| A.10 CHECKSTATUS   | 82 |

|--------------------|----|

| A.11 ACTCNT        | 83 |

| A.12 SEMCNT        | 83 |

| A.13 RDYDEQUEUE    | 83 |

| A.14 SEMDEQUEUE    | 84 |

| A.15 CHGPRI        | 84 |

| A.16 SEMENQUEUE    | 84 |

| A.17 FLGDEQUEUE    | 85 |

| A.18 FLGENQUEUE    | 85 |

| A.19 DTQDEQUEUE    | 85 |

| A.20 DTQRCVENQUEUE | 86 |

| A.21 DTQSNDENQUEUE | 86 |

| A.22 DTQDATA       | 86 |

| A.23 RDYENQUEUE    | 87 |

| A.24 HIGHEST       | 87 |

| A.25 END           | 88 |

| A.26 ENDSWITCH     | 88 |

| Bibliography       | 90 |

| Publications       | 97 |

# List of Figures

| 1.1  | Task sequence                                                             |

|------|---------------------------------------------------------------------------|

| 3.1  | Memory map                                                                |

| 3.2  | Analyzing application program                                             |

| 3.3  | Example of the disassemble                                                |

| 3.4  | Example of selecting multiplexer                                          |

| 3.5  | Example of multiplexer selection                                          |

| 3.6  | Example of selecting multiplexer (Adapted)                                |

| 3.7  | Multicore processor structure                                             |

| 3.8  | Multi core configurator GUI                                               |

| 3.9  | Example of matrix (Multi core)                                            |

| 4.1  | Example of the directives                                                 |

| 4.2  | Example of the directives: Case(1) Both the priority order and fifo order |

|      | are used                                                                  |

| 4.3  | Example of the directives: Case(2) Only the priority order is used 39     |

| 4.4  | Example of the directives: Case(3) Only the fifo order is used            |

| 4.5  | Analyzing process                                                         |

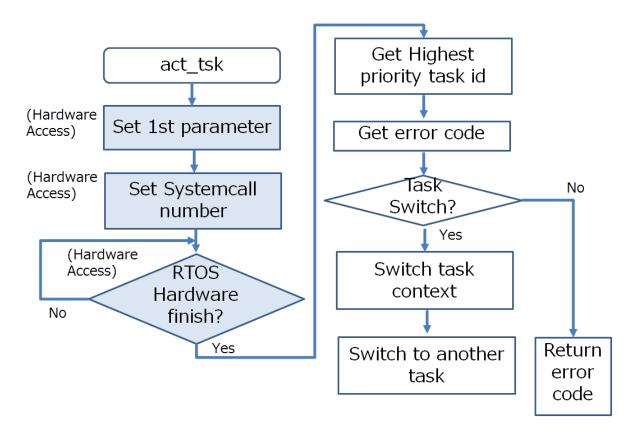

| 4.6  | Hardware implemented part of RTOS system call (act_tsk) 45                |

| 4.7  | Example of system call software part (act_tsk)                            |

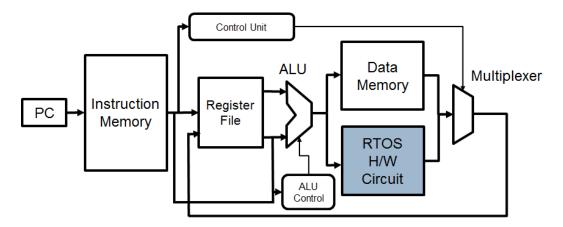

| 4.8  | Processor structure with RTOS hardware                                    |

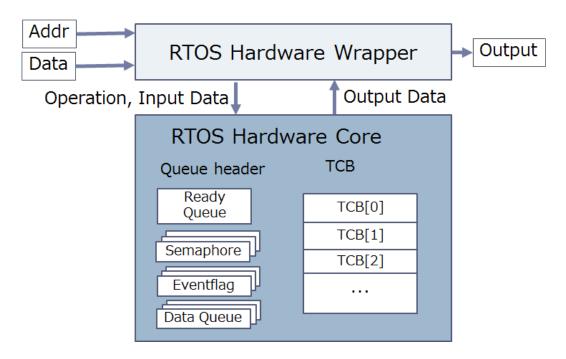

| 4.9  | Structure of RTOS hardware                                                |

| 4.10 | System call software flow                                                 |

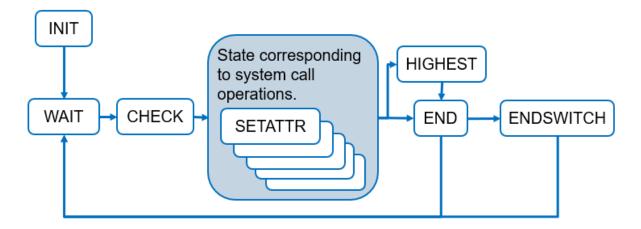

| 4.11 | State transition                                                          |

| 4.12 | TCB structure                                                             |

| 4.13 | Example of a configuration file                                           |

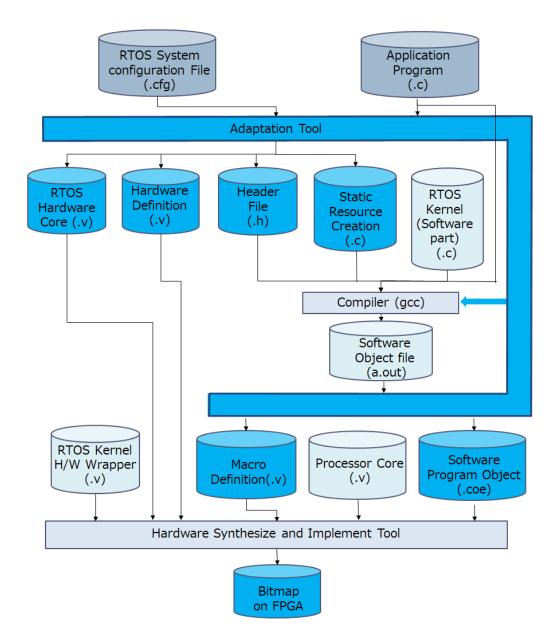

| 4.14 | Development environment                                                   |

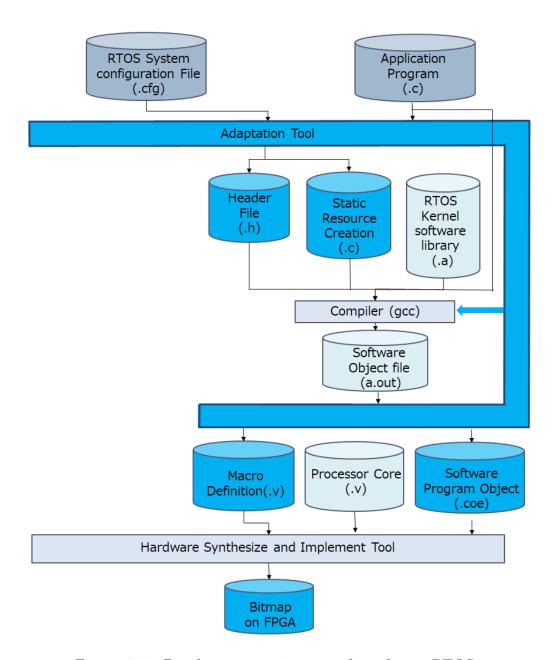

| 4.15 | Development environment for software RTOS                                 |

| 4.16 | GUI tool                                                                  |

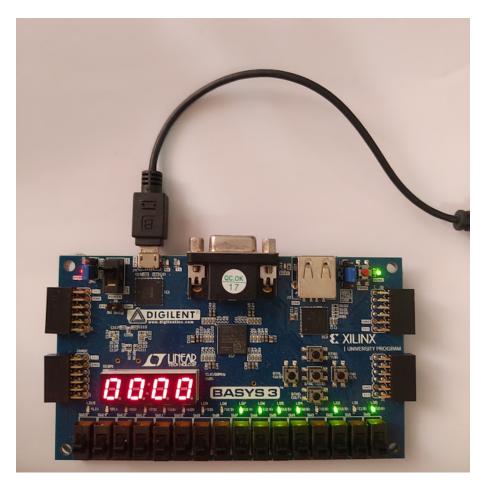

| 5.1  | The Basys3 board                                                          |

# List of Tables

| 2.1  | Comparison of ASIP and the proposed method                           | 10  |

|------|----------------------------------------------------------------------|-----|

| 2.2  | Comparison between OSEK-based configuration and the proposed method. | 11  |

| 2.3  | Comparison in terms of RTOS hardware adaptation                      | 13  |

|      |                                                                      |     |

| 3.1  | Instruction set                                                      | 14  |

| 3.2  | Processor core resources                                             | 27  |

| 3.3  | Processor core resources in detail (Qsort[63])                       | 28  |

| 3.4  | Multicore processor implementation results (1-8 cores) (Matrix)      | 31  |

| 3.5  | 2way 32bit address                                                   | 33  |

| 3.6  | 2way 16bit address                                                   | 33  |

| 3.7  | 1way 32bit address                                                   | 34  |

| 3.8  | 1way 16bit address                                                   | 34  |

|      |                                                                      |     |

| 4.1  | System call and error cause (sig_sem)                                | 41  |

| 4.2  | System call and error cause (isig_sem)                               | 41  |

| 4.3  | System call and error cause (pol_sem)                                | 41  |

| 4.4  | System call and error cause (wai_sem)                                | 42  |

| 4.5  | Addresses for RTOS system calls                                      | 42  |

| 4.6  | States of RTOS hardware wrapper                                      | 44  |

| 4.7  | Operations for RTOS hardware core                                    | 48  |

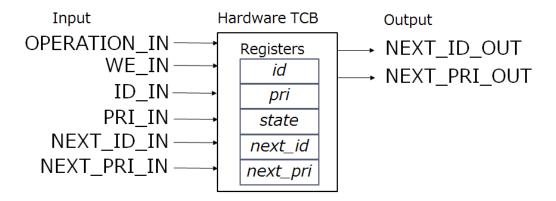

| 4.8  | TCB registers and I/O (Before)                                       | 52  |

| 4.9  | TCB registers and I/O (On queuing)                                   | 52  |

| 5.1  | FPGA resources (semflgdtq)                                           | 64  |

| 5.2  | FPGA resources (semflg, sem02)                                       | 65  |

| 5.3  | FPGA resources (flg02, dtq)                                          | 66  |

| 5.4  | FPGA resources (Cooker, Pot)                                         | 67  |

| 5.5  | FPGA resources (w/o RTOS, Availability)                              | 68  |

| 5.6  | FPGA resources (sem02)                                               | 69  |

| 5.7  | RTOS kernel execution time ( $\mu$ sec)                              |     |

| 5.8  | RTOS kernel execution time in the maximum frequency                  |     |

| 5.9  | RTOS kernel size (bytes)                                             | 73  |

|      | RTOS kernel size (sem02) (bytes)                                     | 74  |

|      | Comparison between automatic and manual adaptation.                  | 74  |

| 0.11 | Comparison between automatic and manda adaptation                    | 1 1 |

| A.1  | INIT                                                                 | 78  |

| A.2  | WAIT                                                                 | 78  |

| A 3  | CHECK                                                                | 79  |

| A.4  | ${ m CTATTR.}$         | 79 |

|------|------------------------|----|

|      |                        | 80 |

| A.6  | EMSTATUS               | 80 |

| A.7  | LGSTATUS               | 80 |

| A.8  | $\Gamma 	ext{QSTATUS}$ | 31 |

| A.9  | HECKTASK               | 31 |

| A.10 | HECKSTATUS             | 32 |

| A.11 | CTCNT                  | 3  |

| A.12 | EMCNT                  | 3  |

| A.13 | DYDEQUEUE              | 3  |

| A.14 | EMDEQUEUE              | 34 |

| A.15 | HGPRI                  | 34 |

| A.16 | EMENQUEUE              | 34 |

|      | - · · · · ·            | 35 |

|      |                        | 35 |

| A.19 | ГQDEQUEUE              | 35 |

|      |                        | 86 |

|      |                        | 86 |

|      |                        | 86 |

| A.23 | DYENQUEUE              | 37 |

| A.24 | [GHEST                 | 37 |

| A.25 | ND                     | 88 |

| A 26 | NDSWITCH               | 39 |

## Chapter 1

## Introduction

## 1.1 Background

In recent years, the use of embedded microprocessors has been increasing with prevailing IoT (Internet of Things). There are too many home appliances with embedded micro processors to list. For example, a smart phone, a television set, a pot, a cooker, a smart speaker, an air conditioner, a printer, a copy machine, a washing machine, a refrigerator, a microwave oven and so on have embedded processors. In an automobile, more than a couple dozen microprocessors are used to control a vehicle. From the perspective of hardware, in the embedded system, when the size of a device and substrate increases, the cost of the appliance also increases so that reducing the size is essential for a product.

Since a processor embedded in an appliance works only for a dedicated system, designing an application specific processor has been studied. ASIP in the literature [1],[2] is one of the examples of a study for such a processor. In the literature [3], to reduce the size of memory, changing the CPU bit-width was studied.

From the perspective of software, RTOS (Real Time Operating System) is commonly used for the embedded system. One of the commonly used RTOS specification is  $\mu$ ITRON in Ref.[4], which has task management functions, task dependent synchronization functions, synchronization and communication functions. With an RTOS, it is possible to easily abstract hardware, use synchronization/communication and benefit from real-time scheduling based on the preemptive and priority-based task scheduling. In addition, a complicated processing can be divided into tasks.

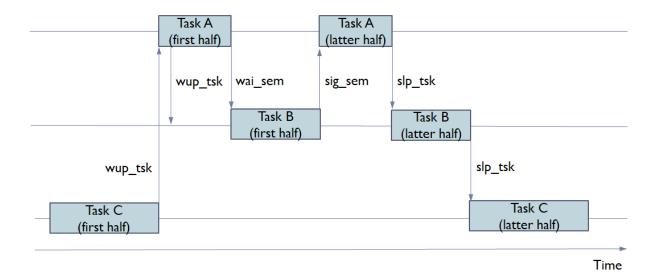

Here, we illustrate a simple example in Fig.1.1 to show the advantages of using task division. There are three tasks, Task A, Task B and Task C. The priority of Task A is the highest, Task B is the middle and Task C is the lowest. We consider the following case. Firstly, Task C works and wakes up Task A. As the priority of Task A is the highest, Task A is executed just immediately after it is woken up. Task A wakes up Task B, but Task B does not work immediately since the priority of Task A is higher than Task B. In execution of Task A, Task A waits for a semaphore due to no resources of the semaphore. As the Task B is ready to execute, Task B is executed and returns a semaphore resource. In this case, Task A resumes executing as Task A is the highest priority. When a procedure of Task A is finished, Task A goes to sleep, then Task B resumes executing. In terminating a procedure of Task B, Task B goes to sleep and Task C executes again. An example of a task code is shown below.

Figure 1.1: Task sequence.

```

Example of a task set (task A) (excerpt).

/* priority: high */

void taska()

{

ER ercd;

while(1) {

/* wait for wake up */

ercd = slp_tsk();

/* wake up task B */

ercd = wup_tsk(TASKB);

/* Process for task A */

/* ... */

/* wait for semaphore */

ercd = wai_sem(SEM_ID1) ;

/* Post process */

/* ... */

}

```

```

Example of a task set (task B)(excerpt).

/* priority : middle */

```

```

void taskb()

{

ER ercd;

while(1) {

/* wait for wake up */

ercd = slp_tsk();

/* Process for task B */

/* ... */

ercd = sig_sem(SEM_ID1) ;

/* Post process */

/* ... */

}

```

```

Example of a task set (task C)(excerpt).

/* priority : low */

void taskc()

{

ER ercd;

while(1) {

/* Process for task C */

/* ... */

/* wake up task A */

ercd = wup_tsk(TASKA);

/* Post process */

/* ... */

}

}

```

taska(),taskb(), and taskc() are the source code of Task A, Task B, and Task C, respectively. Initially all tasks are started, but Task A and Task B go to the sleep state, so that Task C starts to execute as Fig.1.1. Each task invokes system calls to behave as described above. The source code reveals that just invoking system calls can realize the task transition. An example of implementing the same procedure without using RTOS is as follows.

```

Example of a procedure w/o RTOS (main).

int firstflag_a = TRUE; /* TASK A */

```

```

int firstflag_b = TRUE; /* TASK B */

int firstflag_c = TRUE; /* TASK C */

int state_taska = NOTREADY;

int state_taskb = NOTREADY;

int state_taskc = READY;

int sem1 = 0; /* semaphore */

int main()

{

while(1) {

if (state_taska == READY) {

taska();

} else if (state_taskb == READY) {

if (state_taska == WAIT) {

taska();

}

taskb();

} else if (state_taskc == READY) {

if (state_taska == WAIT) {

taska();

if (state_taskb == WAIT) {

taskb();

taskc();

} else {

/* there is no ready task */

continue;

}

return(0);

}

```

```

void taska()

{

if (firstflag_a == TRUE) {

/* first half */

firstflag_a = FALSE;

if (sem1 == 0) {

/* semaphore is not acquired */

/* return to the main loop */

```

```

/* task A state is WAIT */

state_taska = WAIT;

return;

} else {

/* semaphore is acquired */

sem1 = 0;

/* do a job for Task A */

/* finish task A */

/* As latter half of task A is finished, */

/* do again from the first half */

firstflag_a = TRUE;

state_taska = NOTREADY;

return;

}

} else {

/* latter half */

if (sem1 == 0) {

/* semaphore is not acquired */

/* return to the main loop */

/* task A state is WAIT */

state_taska = WAIT;

return;

} else {

/* semaphore is acquired */

sem1 = 0;

/* do a job for Task A */

/* finish task A */

/* As latter half of task A is finished, */

/* do again from the first half */

firstflag_a = TRUE;

state_taska = NOTREADY;

return;

}

}

```

```

Example of a procedure w/o RTOS (Task B).

void taskb()

{

if (firstflag_b == TRUE) {

/* first half */

firstflag_b = FALSE;

```

```

/* Return semaphore to execute task A */

sem1 = 1;

return;

} else {

/* latter half */

firstflag_b = TRUE;

/* task B is finished */

state_taskb = NOTREADY;

return;

}

```

```

Example of a procedure w/o RTOS (Task C).

void taskc()

{

if (firstflag_c == TRUE) {

/* first half */

firstflag_c = FALSE;

/* wake up task A */

state_taska = READY;

/* wake up task B */

state_taskb = READY;

return;

} else {

/* latter half */

firstflag_c = TRUE;

return;

}

}

```

taska(),taskb(), and taskc() are functions working in a similar way. As can be seen from the code, it needs global variables to control the task behavior, such as firstflag\_a, firstflag\_b, firstflag\_c, state\_taska, state\_taskb and state\_taskc. As each function executes two parts of the function, firstflag\_a, firstflag\_b and firstflag\_c are used for controlling the task transition. state\_taska, state\_taskb and state\_taskc store the current task state. sem1 is used to store the count of the semaphore. In addition main function is necessary to invoke each procedure. Generally speaking, it is recommended that the module coupling should be low in designing software, whereas the example without RTOS needs several global variables to control and communicate functions, so that high module coupling is inevitable. In an actual system, much more global variables are necessary so that the source code will become more complicated, which makes readability and maintainability worse.

As explained above, using RTOS has advantages to developing embedded systems. In the literature [5], the advantages and disadvantages of using RTOSs for small microcontroller system development are discussed. The literature illustrates that software productivity can be improved with using RTOSs in system development. However, when RTOSs are used for small microcontrollers, the literature also described disadvantages that an RTOS itself consumes additional memory, computational resources and power. As an example of a small microcontroller, the flash ROM size of a microcontroller family in Ref.[6], having various applications, ranges from 1Kbyte to 512Kbytes, which cannot be ignored for the memory consumption of an RTOS kernel.

Since using RTOS has benefit in designing embedded applications as mentioned above, our motivation for the research comes from the requirement for mitigating overhead of an RTOS. An RTOS kernel following  $\mu$ ITRON4.0 specification in Ref.[7] is usually provided as a library format, so that only specific system calls which are actually used in an application program are linked with an application program, which means a program code for unused system calls does not occupy the memory space. However, the unit of the selection of codes is a whole system call, which is too rough for the limited memory resource. In order to reduce the overhead of software part, hardware RTOS is effective. Since hardware resource is related to cost of the production, reducing hardware resources is also required. Based on the points above, when an application program is fixed, our research objectives are as follows.

- Build an application adaptive processor core.

- Remove unused codes in RTOS kernel, while leaving necessary functions such as checking possible errors.

- Implement hardware RTOS to reduce the amount of software resources and execution time.

- Remove unused codes in a hardware RTOS as well as a software-only RTOS.

- Build automatic development environment with which we can perform the items above.

In this dissertation, in order to evaluate the proposed method, we implement a product to which adaptation is applied on an FPGA device. While FPGA devices including microprocessor hard cores are prevailing in recent years, since the target of this study includes small/low-cost IoT devices, we consider low-cost FPGA devices without microprocessor hard cores as the subject of this dissertation. Here, we call it "adaptation" to eliminate unnecessary functions for an application. A product to which adaptation is applied is called an "adaptive" or "adapted" product. The following Chapters explain our proposal to achieve the objectives above in detail.

### 1.2 Contribution

Since the process described in this dissertation can be applied for generating an application adaptive processor core and RTOS, the main contribution of this dissertation is summarized as follows.

- Propose a method for generating an application adaptive processor core automatically.

- Illustrate how we configure a fine-grained RTOS kernel.

- Explain the way to create hardware RTOS and configure application adaptive hardware RTOS automatically.

- Show the automatic development environment.

Since the number of IoT devices including processors is increasing extremely, a development environment for producing low cost and effective devices in a short period of time is desired. Recently, advances of technology make it possible to implement functions which a target system needs in a device, which is called SoC (System on Chip). While functions embedded in a device depend on a target system, a processor core and RTOS are commonly used technology so that it can be said that this dissertation contributes to revealing the method for creating application adaptive devices.

### 1.3 Structure of Dissertation

This dissertation is organized as follows. Related work regarding adaptation of a processor core and OS kernel, software overhead mitigation, and hardware implementation for RTOS functions is reviewed in Chapter 2. We explain about construction of automatic development environment for adaptive processor core in Chapter 3. In this chapter, a processor structure for our target is explained and how we analyze an application program and construct an adapted processor core for the application is illustrated. In Chapter 4, we propose a framework for building fine-grained RTOS including software adaptation and hardware adaptation. For software adaptation, we describe a method for building an application adapted system call. For hardware adaptation, the way of implementing RTOS functions as hardware and the method for building an application adapted hardware are proposed. Chapter 5 shows the effect of RTOS configuration, which includes an evaluation for hardware resource usage, software size for system calls, and system call execution time. Finally, in Chapter 6, we summarize this dissertation and discuss about future work.

## Chapter 2

## Related Work

### 2.1 Related Work

In this chapter, we review related works for this dissertation. As there are several approaches to customize microprocessors according to a requirement, we oversee studies for processor core adaptation. Then the overviews of RTOS related adaptation are summarized. First, the way of RTOS kernel adaptation in software is described. Next, several researches regarding that a part of functions of an RTOS is implemented in hardware are shown as a method for software overhead mitigation. Especially, a hardware scheduler has been studied since scheduler is a core component of an RTOS, so that we review previous studies for a hardware scheduler. Finally, we explain studies for implementing a whole RTOS system call function in hardware.

## 2.1.1 Processor Core Adaptation

For a processor core embedded in an FPGA, there are two ways to implement one: hard macro processors and soft macro processors. While hard-macro processors are built-in along with FPGA resources, soft processors are constructed with programmable resources in an FPGA. Cortex-A9 in Zynq-7000 in Ref.[8] is an example of a hard-macro processor. Hard processors have an advantage in performance and size while they are not flexible for changing structures. On the other hand, MicroBlaze of Xilinx in Ref.[9] and NiosII of Intel in Ref.[10] are examples of soft processors provided as software macro IP in an FPGA. Soft processors are configurable so that they can be customized according to running applications and can be extended with acceleration circuits if necessary.

To create an application specific processor, there are several approaches as follows. ASIP (Application-domain Specific Instruction-set Processor) is a technology for building a processor which is optimized for an application program. ASIP methodologies are surveyed in the literature [1],[2]. Table 2.1 summarizes a comparison of features between ASIP and the proposed method. For generating an application specific processor, ASIP needs to analyze an application program manually and create a tool set including a compiler for the processor. For creating the tool set, ASIP provides a tool called ASIP Meister, which has an interface to input the register length, the number of registers and the number of pipeline stages. Xtensa of Tensilica in the literature [11] is a commercial processor which can be customized for target applications. This processor can be optimized for an

Table 2.1: Comparison of ASIP and the proposed method.

| Feature              | ASIP[2]                                | Proposed Method                  |

|----------------------|----------------------------------------|----------------------------------|

| Program analysis     | Manual                                 | Automatic                        |

| Generate a processor | Manual translation to ADL <sup>1</sup> | Generate by a tool               |

|                      | ADL is synthesized to HDL              |                                  |

| Instructions         | Add dedicated instructions             | Use existing instructions        |

| Registers            | Add special purpose registers          | Not add new registers            |

| Development tool set | Need to extend an existing             | Able to use an existing tool set |

|                      | tool set for new instructions          |                                  |

embedded application by sizing and selecting features and adding new instructions. The literature [3] proposed to change the CPU bit-width to reduce the size of memory in a processor. In these approaches, the processor needs to be tuned manually. As another approach, selecting a subset of instructions from an existing instruction set is introduced in the literature [12],[13]. In this approach, existing software development tools including compilers can be applied. The techniques for selecting instructions show that the selection according to application programs simplifies the processor's microarchitecture and reduces the amount of hardware resources and it is illustrated that about 50% of instructions among the full instruction set are actually used for several applications, and that the method is effective in reducing area and improving clock speed in the evaluation result. In their study, the analysis of program codes does not take into account dependency between instructions which determines necessity of forwarding paths. (That is, forwarding logic is always equipped even when it is unnecessary for the program.)

## 2.1.2 RTOS Kernel Adaptation

While an RTOS kernel software is usually provided as a library format, that is not enough for adapting to an application program. The configuration of an RTOS kernel adapted to an application system has been studied. In the literature [14], techniques for automatically reducing the memory footprint of general-purpose operating systems on embedded platforms are described. In this literature, hand-written assembly codes in the kernel are analyzed with a decompilation technique, and unused codes and duplicated codes are eliminated. However, as the target operating system of this literature is Linux, the meaning of unused codes is different from ours. In order to build an application specific RTOS kernel, OSEK in Ref. [15], which is an RTOS kernel commonly used in the automotive industry, defines OIL (OSEK Implementation Language) for description of application specific objects. This description is used as system configuration information, and a configurator generates a tailored RTOS which consists only of application specific objects and actually-used system calls. The literature [16] describes an example of OSEK-based RTOS, the main objective of which is to verify a generated RTOS, where configuration information and application codes are analyzed and an OS-application interaction graph is extracted for verification. Table 2.2 shows comparison between OSEK-based adaptation and our proposed method in terms of the level of RTOS kernel adaptation.

<sup>&</sup>lt;sup>1</sup>Architecture Description Language

Table 2.2: Comparison between OSEK-based configuration and the proposed method.

| Feature         | OSEK-based[15][16]       | Proposed Method                     |

|-----------------|--------------------------|-------------------------------------|

| RTOS adaptation | Object/System call level | Code-fragments (Fine-grained) level |

### 2.1.3 Software Overhead Mitigation

In order to mitigate software overhead in terms of resources and latency when RTOS is used, implementing some of the functions as hardware has been studied. SoCLC (SoC Lock Cache) hardware mechanism to improve the performance of lock latency is proposed in the literature [17],[18] and its framework for designing is explained in the literature [19]. A modular microkernel architecture in hardware is demonstrated in the literature [20]. In the literature [21], a configurable hardware scheduler architecture is presented. This scheduler provides three scheduling disciplines: priority-based, rate monotonic and earliest deadline first. This shows the advantage of modularity and the improvement of the performance. In the literature [22], three scheduler models are implemented: (i) Sorts (Software Real-Time Scheduler), (ii) Co-Sorts (Co-processor Software Real-Time Scheduler), and (iii) HaRTS (Hardware Real-Time Scheduler). It is concluded that Co-SoRTS and HaRTS present the best results for hard real-time applications, while SoRTS is suitable for soft real-time systems. The literature [23] and [24] show an ITRON based RTOS extended to support multithread processing for Responsive Multithreaded (RMT) Processor. As this implementation is dedicated to an RMT processor, the approach is different to a general-purpose processor.

#### 2.1.4 Hardware Scheduler

A hardware scheduler with a new task-queue architecture to support various scheduling algorithms such as time sliced priority scheduling, Earliest Deadline First, and Least Slack Time is described in the literature [25]. RT-SHADOWS in the literature [26],[27] is a hardware scheduler and APIs to provide hardware multi-thread support, which is a subset of the task management APIs. In the literature [28], with SOPC (System On Programmable Chip), an architecture that co-schedules hardware and software with RTOS was discussed. The literature [29] and [30] proposed an interrupt scheduler called REMON (Real-Time Embedded Monitor). The scheduler is implemented in hardware to improve performance in executing switching of the ISR (Interrupt Service Routine). While this proposal implemented the scheduler in hardware, other functions of RTOS were not implemented in hardware. In the literature [31], earliest deadline first (EDF) scheduler is implemented in hardware. The literatures [32] and [33] show the method and evaluation result of implementing the scheduler function of TinyOS, an OS for sensor nodes. All the hardware implementations mentioned above are only for performance improvement and do not take adaptability to a target application into account.

#### 2.1.5 Hardware RTOS

There are several studies for implementing a whole RTOS system call function in hardware. Silicon TRON in the literature [34],[35],[36],[37] provides basic functionalities of

$\mu$ ITRON in hardware as a peripheral chip and the performance was evaluated in the literature [38]. The literature [39] explained that a part of  $\mu$ ITRON functions, such as task management, task dependent synchronization functions, semaphore, eventflag, and interrupt management were implemented in hardware. The literature [40] shows an idea for extracting RTOS kernel functions from UML description of an application program, whereas the detailed method was not described. In the literature [41], a real-time kernel coprocessor is implemented in an ASIC, which is called RTU. It has eight priorities and RTOS functions such as semaphore, eventflag, watchdog and priority preemptive scheduling. A real-time multithreaded operating system kernel, hthreads, is presented in the literature [42]. It has a shared memory programming model similar to POSIX Threads. In the system on CPU/FPGA chips, hardware threads and software threads can exist and they are scheduled by a hardware scheduler component, which performs first-in-first-out, round robin and priority-based scheduling algorithms. In the literature [43], general-purpose RTOS functions with API interfaces and a dedicated CISC processor are implemented in an FPGA. ARTESSO [44],[45],[46] is a hardware RTOS, which provides more than 30 system calls. The specific feature of the RTOS hardware is a Virtual Queue, which is a queue structure with a tournament circuit to select an element in the queue. They enhanced the architecture to a multi-core processor in the literature [47] and studied to implement on ARM-based SOC in the literature [48], [49]. However, these RTOSs do not have a function to adapt to an application program automatically.

### 2.1.6 Adaptation for Hardware RTOS Functions

Simple and Effective hardware based Real-Time Operating System (SEOS) in the literature [50] provides adaptability for hardware RTOS. SEOS adaptation consists of hardware and software processes. However, these processes need to be applied manually. In the literature [51], OSEK-based RTOS hardware, called OSEK-V processor, is implemented with an application system after analysis of the application program, but it is not flexible to updates of the application. In the literature [52], a method of generating full hardware implementation where tasks as well as RTOS are implemented in hardware is described. To synthesize tasks for hardware, there is some restriction to tasks (e.g., no mutual exclusion). In this literature, adaptation of RTOS is not described. It is described that error checking in act\_tsk takes 21 cycles while only 1 cycle is needed with our method and also unused hardware resources can be deleted in our method. Table 2.3 shows comparison in terms of RTOS hardware adaptation.

While studies for implementing RTOS functions in hardware mentioned above have been conducted for several years, we have been studying to reduce runtime and resource overhead by adapting RTOS kernel functions and processor functions to an application program. We confirmed an effect of implementing a primitive RTOS kernel operation as hardware in the literature [53]. After that, we proposed a hardware RTOS implementation in a system-call level in the literature [54]. However, automatic adaptation environment is not shown in the literature. In this dissertation, we explain our method for developing an application-specific system with RTOS in detail.

Table 2.3: Comparison in terms of RTOS hardware adaptation.

| Feature         | SEOS[50]            | OSEK-V[51]         | Ref.[52]       | Proposed Method     |

|-----------------|---------------------|--------------------|----------------|---------------------|

| Specification   | SEOS                | OSEK               | TOPPERS/APS3   | $\mu$ ITRON4.0      |

| Processor       | NIOS-II             | Tailoring based on | No CPU         | MIPS32              |

|                 |                     | Rocket RISC-V      |                |                     |

| Platform        | Altera Cyclone-II   | Xilinx Zynq-7020   | Xilinx Artix-7 | Xilinx Artix-7      |

| Software Part   | Simple API for      | No software        | No software    | Simple API for      |

|                 | interfacing purpose | part               | part           | interfacing purpose |

| Hardware Part   | Major OS            | All of             | All of         | Major OS            |

|                 | functionalities     | OSEK system        | RTOS system    | functionalities     |

| RTOS Adaptation | Manual              | Automatic          | No adaptation  | Automatic           |

## Chapter 3

# Construction of Automatic Development Environment for Adaptive Processor Core

### 3.1 Structure of Processor Core

The techniques presented in Sections 3.1 to 3.5 are ones proposed in the author's literature [55],[56],[57]. In this study, we adopted MIPS architecture for a processor core since the architecture is well-known and is commonly used in the market. The structure of a processor core is 5-stage pipeline and the instruction set architecture is MIPS32 in Ref.[58]. The feature of the processor core we implemented is explained below.

#### Instruction set

We implemented all of the instructions on the core instruction set in the literature [59] except for load link instruction (11) and store conditional (sc), which are instructions for a multi-processor core. Additionally, as the compiler (GCC) outputs several instructions which are not on the list of the literature [59], the instructions, xor, xori, sra, sllv, srav, srlv, srav, srlv, bgez, bltz, blez, bgtz, jalr, lb, and lh, are also implemented. To execute multiplication and division, we implemented the instructions related to these operations, mult, multu, div, divu, mfhi and mflo. mfc0 is also implemented for a processor control. All instructions we implemented are shown in the table 3.1.

Table 3.1: Instruction set.

| Category                 | Instruction | Description            |

|--------------------------|-------------|------------------------|

| Arithmetic operation add |             | Add                    |

|                          | addu        | Add unsigned           |

|                          | addi        | Add immediate          |

|                          | addiu       | Add immediate unsigned |

|                          | and         | And                    |

|                          | andi        | And immediate          |

|                          | sub         | Subtract               |

|                          | subu        | Subtract unsigned      |

continue to the next page

| Category          | Instruction | Description                             |

|-------------------|-------------|-----------------------------------------|

|                   | lui         | Load upper immediate                    |

| Logical operation | nor         | Nor                                     |

|                   | or          | Or                                      |

|                   | ori         | Or immediate                            |

|                   | xor         | Exclusive or                            |

|                   | xori        | Exclusive or immediate                  |

| Comparison        | slt         | Set on less than                        |

|                   | sltu        | Set on less than unsigned               |

|                   | slti        | Set on less than immediate              |

|                   | sltiu       | Set on less than immediate unsigned     |

| Shift             | sll         | Shift left logical                      |

|                   | sra         | Shift right arithmetic                  |

|                   | srl         | Shift right logical                     |

|                   | sllv        | Shift left logical variable             |

|                   | srav        | Shift right arithmetic variable         |

|                   | srlv        | Shift right logical variable            |

| Branch            | beq         | Branch on equal                         |

|                   | bne         | Branch on not equal                     |

|                   | bgez        | Branch on greater than or equal to zero |

|                   | bltz        | Branch on less than zero                |

|                   | blez        | Branch on less than or equal to zero    |

|                   | bgtz        | Branch on greater than zero             |

| Jump              | j           | Jump                                    |

| 1                 | jal         | Jump and link                           |

|                   | jalr        | Jump and link register                  |

|                   | jr          | Jump register                           |

| Load              | lb          | Load byte                               |

|                   | lbu         | Load byte unsigned                      |

|                   | lh          | Load halfword                           |

|                   | lhu         | Load halfword unsigned                  |

|                   | lw          | Load word                               |

| Store             | sb          | Store byte                              |

| 50010             | sh          | Store halfword                          |

|                   | sw          | Store word                              |

| Multiplication    | mult        | Multiply                                |

| Waterpheadon      | multu       | Multiply unsigned                       |

| Division          | div         | Divide                                  |

| 21/101011         | divu        | Divide unsigned                         |

| Register transfer | mfhi        | Move from high                          |

| regioner manorer  | mflo        | Move from low                           |

| Control           | mfc0        | Move from coprocessor                   |

| Common            | штсо        | MOVE HOLL COPLOCESSOI                   |

#### 5-stage pipeline

The processor core we implemented consists of the five stage pipeline, IF (Instruction Fetch), ID (Instruction Decode), EX (Execution), MEM (Memory Access), and WB (Write Back to a register) stages. IF is the stage for reading an instruction from the instruction memory according to PC (Program Counter). With our implementation, since a program for the processor is stored in a block memory on an FPGA in advance, the instruction indicated by PC is read in synchronization with the clock. ID is a stage for decoding the instruction and setting necessary controls to execute the instruction correctly. With this implementation, a decision for whether a branch is taken or not is made in the ID stage. EX is a stage for working ALU (Arithmetic Logic Unit), the unit for arithmetical or logical operations, and the unit for multiplication or division. MEM is a stage for reading data from or writing to the data memory according to the address calculated in the previous stage. WB is a stage for writing the calculated result back to a register.

#### Branch decision

When a conditional branch instruction is executed, the decision of whether the control proceeds to the following instruction (not-taken) or branches (taken) is made in ID stage.

#### **Delay Slot**

A conditional/unconditional branch instruction has one delay slot, so that the following instruction of a branch instruction is always executed regardless of the branch decision. We do not need to flush or stall an instruction in the delay slot. When a jump and link instruction (jal, jalr) is executed, the return address for the instruction is the address of PC+8.

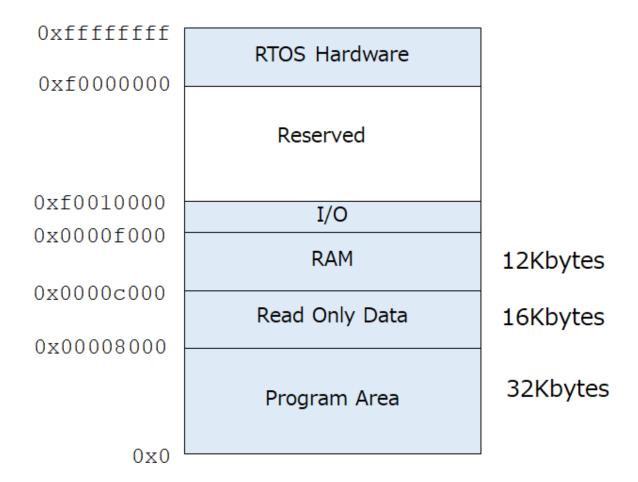

#### Memory Map

The processor core we developed has 32Kbytes program area which is implemented with a block memory configured as a single port ROM in the FPGA. Read-only data such as a variable with constant expression is also stored in a block memory in the FPGA and can be accessed with the addresses from 0x8000 to 0xbfff (16Kbytes). For variable data, RAM area which can be accessed with the addresses from 0xc000 to 0xefff (12Kbytes) is implemented in the logic block in the FPGA. I/O area such as the address of UART control is memory mapped to the addresses from 0xf000 to 0xffff. RTOS hardware can be accessed with the addresses from 0xf0000000 to 0xffffffff, which is explained in Section 4.1 in detail. This memory map is summarized in the Fig.3.1.

#### Forwarding Unit

When an instruction uses the results of the former instructions, the pipeline processing does not have to be stalled as long as the results can be obtained via the pipeline registers even if it has not been written back to general-purpose registers. The forwarding unit detects these cases.

Figure 3.1: Memory map.

#### Detection of pipeline stall

When an instruction uses the results of the former instructions but the forwarding unit cannot supply the results immediately, the pipeline has to be stalled. The pipeline-stall-detection unit decides and controls the pipeline stall.

#### **Clock Generation**

We implemented the hardware circuit to an FPGA of Xilinx and used a clock generation IP on the FPGA to convert the clock rate. The frequency of the clock source of the FPGA is 100MHz and we used the clock generation IP to acquire a proper clock rate to execute our target program.

#### **UART** Interface

In order to output data from the processor core, we implemented UART interface through the IO pin of an FPGA board and the data can be acquired with a terminal soft on PC.

#### 7-Segment display and LEDs

On the FPGA board we used for the evaluation, Digilent Basys3 in Ref.[60], there are 4-digit 7-segment display and 16 user LEDs. These I/O addresses are mapped to memory addresses to access these 7-segment display and LEDs, so that a write access to a designated address enables an application program to turn the 7-segment display or LEDs on.

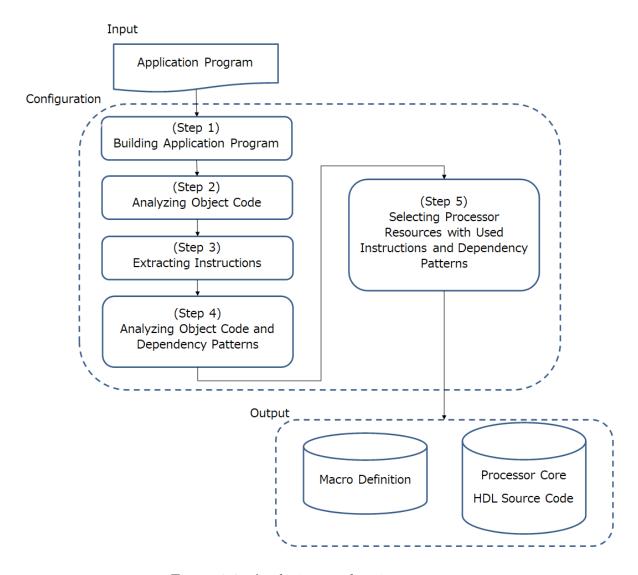

## 3.2 Analyzing Application Program

In order to generate an application adaptive processor core, we proceed to the following steps. (Fig.3.2)

- (Step 1) An object file for an application program is built. (Section 3.2.1)

- (Step 2) An object file for the application program is analyzed. (Section 3.2.2)

- (Step 3) Used instructions are extracted. (Section 3.2.3)

- (Step 4) The object code is analyzed and the dependency patterns are searched. (Section 3.2.4)

- (Step 5) Processor resources with used instructions and dependency patterns are selected. (Section 3.3)

These steps are also applied to our environment illustrated in Section 4.5.

## 3.2.1 Building Application Program

Source codes of an application program which are written in C language or MIPS assembly language are input, and C compiler is invoked to create an object file in executable format. In our implementation, GCC compiler for MIPS is used.

## 3.2.2 Analyzing Object Code

After an executable object file is generated, an assembly code is extracted from the object file. As we compile the source code with GCC compiler, the objdump command in GCC compiler utility is available for the disassembling.

## 3.2.3 Extracting Instructions

From the result of disassembling, actually used instructions are extracted and resources of a processor core to be used by the application program are determined. In disassembling the code which has been generated on the first step, the result such as Fig.3.3 is output and the instruction field is extracted to examine what instruction is used. We created a list of instructions and resources in advance and the list shows which resources are actually used for each instruction in an application program.

Figure 3.2: Analyzing application program.

## 3.2.4 Analyzing Object Code and Dependency Patterns

In this implementation of the processor core, to detect forwarding and hazard, the forwarding detection unit and hazard detection unit have to be implemented, whereas, if there is no code sequence causing forwarding or hazard, we can omit the circuit of the corresponding detection unit.

In this step, possibility of forwarding and pipeline stall is detected. The instruction sequence for dependency between instructions is searched, then the necessity of each forwarding or pipeline stall unit is decided. If some forwarding or pipeline stall patterns are found not to occur, the corresponding forwarding units or stall detection circuits are removed from the processor circuit. The details about the correspondence between dependency patterns and forwarding/stall detection units are described below, which is based on the literature [61].

```

Example of Disassemble -

00000288 <main>:

288: 27bdffe0

addiu $29,$29,-32

28c: afbf001c

sw $31,28($29)

290: afb00018

sw $16,24($29)

294: 40806000

mtc0 $0,$12

298: 3c020001

lui $2,0x1

29c: ac40c034

sw $0,-16332($2)

2a0: 3c020001

lui $2,0x1

2a4: ac40c010

sw $0,-16368($2)

2a8: 3c020001

lui $2,0x1

2ac: ac40c004

sw $0,-16380($2)

2b0: 3c020001

lui $2,0x1

2b4: ac40c02c

sw $0,-16340($2)

2b8: 3c020001

lui $2,0x1

2bc: ac40c014

sw $0,-16364($2)

```

Figure 3.3: Example of the disassemble.

#### Dependency related to forwarding units

When an instruction uses the result of the former instructions, the forwarding unit detects the necessity of forwarding and designates the forwarding paths. If such dependencies are not found, the forwarding detection unit and the corresponding paths can be removed.

Forwarding patterns are classified into five cases in our processor core.

1. Forwarding ALU result to the next instruction: When the result of ALU calculation is used in the next instruction, the result is forwarded to the next instruction via a pipeline register. An example is as follows.

```

add $10, $8, $9

sub $12, $10, $11

```

The two instructions, add and sub, have data dependency with respect to \$10. The forwarding unit detects the dependency in the instruction sequence and controls the forwarding paths so that sub in EX stage immediately receives the result of add residing in MEM stage.

2. Forwarding ALU result to the instruction immediately after the next instruction:

When the result of ALU calculation is used in the instruction immediately after the next instruction, the result is forwarded to the instruction. An example is as follows.

```

add $10, $8, $9

sub $14, $13, $12

lw $11, 0($10)

```

In this example, lw uses the result of add for address calculation. This type of dependency is solved by forwarding the value in WB stage to EX stage.

3. Forwarding ALU result to conditional branch instruction: When the result of ALU calculation is used in the conditional branch instruction just after the next instruction, forwarding from MEM stage to ID stage is performed. An example is as follows.

```

add $10, $8, $9

sub $14, $13, $12

beg $10, $11, label

```

4. Forwarding ALU result to the following store instruction: When the result of ALU calculation is used in the next store instruction as the stored value, the value in WB stage is forwarded to MEM stage. An example is as follows.

```

add $10, $8, $9 sw $10, 0($11)

```

5. Forwarding from jal, jalr: Jump and link instructions (jal, jalr) write the return address in \$31 register. When the jump target instruction is a jump register instruction (jr) with \$31, the return address being written in \$31 is forwarded to jr. An example is as follows.

```

jal label

nop

label:

jr $31

```

#### Dependency related to stall detection units

When an instruction uses the result of the previous instruction but the forwarding unit cannot supply it immediately, the necessity of pipeline stall is detected by the stall detection unit. If such dependency is not found in the application program, the stall detection circuits can be removed.

There are five cases where the pipeline stalls.

1. Result of load instruction used by the next instruction: When the result of a load instruction is used by the next instruction, the pipeline has to be stalled. An example is as follows.

```

lw $8 0($9)

add $9, $8, $10

```

In this case, after add is stalled in ID stage for one cycle while lw advances, it receives, in EX stage, the value forwarded from WB stage.

2. Result of ALU/load instruction used by the next conditional branch: When the result of ALU calculation or the load instruction is used in the next conditional branch instruction, pipeline has to be stalled. An example is as follows.

```

add $10, $8, $9

beq $10, $11, label

```

In this case, beq stalls in ID stage for one cycle and is given the value from MEM stage. If the prior instruction is 1w, it needs two-cycle stalling.

3. Result of load instruction used by conditional branch after the next instruction: When the result of a load instruction is used in a conditional branch instruction after the next instruction, the pipeline has to be stalled for one cycle. An example is as follows.

```

lw $10, 0($9)

nop

beq $10, $11, label

```

beq stalls in ID stage for one cycle and is given the value from WB stage.

4. Result of ALU used by jr or jalr: When the result of ALU calculation is used in the next jump register or jump and link register instruction, the pipeline has to be stalled. An example is as follows.

```

add $10, $8, $9 jr $10

```

In this case, jr stalls in ID stage for one cycle.

5. Result of load instruction used by jr or jalr after the next instruction: When the result of a load instruction is used in jr or jalr after the next instruction, the pipeline has to be stalled. An example is as follows.

```

lw $10, 0($9)

nop

jr $10

```

In this case, jr stalls in ID stage for one cycle.

## 3.3 Selecting Processor Resources with Used Instructions and Dependency Patterns

Resources/components which are required for each instruction to be executed are listed in advance. Similarly, the information about the units necessary for solving dependencies is prepared. Using this list and information for correspondence between instructions/sequences and necessary components, once the analysis in the previous section is done, all the processor resources for running the application program are fixed. The target resources for configuration are described below.

- 1. *multiplexer*: There exist several multiplexers in the processor core. Whether each multiplexer is used or not depends on the selected instructions. If some instructions are not actually used for the application program, the corresponding multiplexers, related data paths, and control logic are removed.

- 2. Adder for PC: When a branch is taken, an adder is used to calculate the branch target address. The current program counter value plus four (instruction size) and immediate value are added. This adder is removed if the target program does not include branch instructions, although it is not likely to happen.

- 3. Comparator for equality condition: Comparators for equality condition are used for beq, bne instructions. If branch instructions with equality condition are not included in the application, the comparators are removed.

- 4. Comparator for positivity condition: A comparator for positive condition is used for bgez and bltz instructions. If the application does not include branch instructions with positivity condition, this comparator is removed.

- 5. Comparator for negativity condition: A comparator for negativity condition is used for blez and bgtz instructions. If branch instructions with negativity condition do not appear, the comparator is removed.

- 6. *Multiplier*: A multiplier is used for multiplication. If the application does not include multiplication instructions, this component is eliminated.

- 7. *Divider*: A divider is used for division. Embedded applications tend to avoid integer division. Therefore, this is removed for many applications.

- 8. Forwarding unit: As described in Section 3.2.4, there are five cases for the forwarding to work. While each case involves its detection circuit and related connections, we remove them if the forwarding never happens.

- 9. Stall detection unit: There are five cases where the pipeline has to be stalled as described in Section 3.2.4. While each case needs its detection circuit and related connections, we remove them if the case is never met.

Figure 3.4: Example of selecting multiplexer.

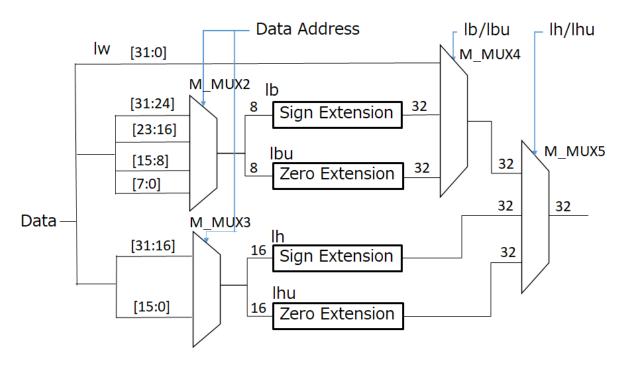

## 3.4 Generating Application Adaptive Processor Core Circuit

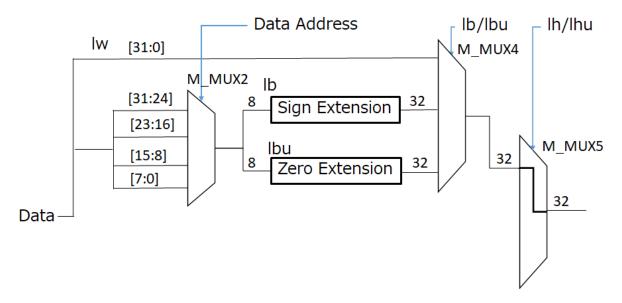

For the resources described in the previous section, from the result of disassembling an application program, actually used resources for the application program are selected. Processor core descriptions and a macro definition file are the output in the previous step. Selected resources for the processor configured for the target application are indicated by the macro definition file. Figure 3.4 illustrates a part of the processor data path with multiplexers, which are used for a byte data selection with the load instruction. The multiplexer M\_MUX2 is not used if there is not load byte data instruction in an application program and the multiplexer M\_MUX3 is not used if there is not load half word data instruction in an application program. In addition, in the case that there is not load byte data, the selection of M\_MUX4 is not necessary. In order to make this selection possible, a directive is inserted in the source code of the processor core described in HDL (Verilog) in advance as the code of Fig.3.5.

In the case that M\_MUX3 in Fig.3.4 is not used in an application program, memmux\_3\_nouse is defined if there is not load half word instruction. On the other hand, if load half word data is used, memmux\_3\_mux is defined. These defines are an output of a configuration tool. Other resources are selected in a similar way. In the case that half word instruction is not used in an application program, the circuit block becomes as in Fig.3.6. As we can see from the figure, multiplexers, M\_MUX3 and M\_MUX5 are removed from the processor core, which contributes to reducing the size of the processor core circuit.

Macro names are expressed in the format:

<sup>&#</sup>x27;define Stage\_ResourceNo\_Selection

Figure 3.5: Example of multiplexer selection.

The Stage part is as follows.

```

ID stage idmux

EX stage exmux

MEM stage memmux

WB stage wbmux

```

ResourceNo is a sequential number of each resource. If a multiplexer is selected, mux or mux3 (for 3-to-1 multiplexer) is specified for selection. Otherwise, nouse is for the unused multiplexer.

Using the results of the analysis process, the configurator makes a macro definition file as follows.

```

'define idmux_1_mux3

'define idmux_2_mux

'define idmux_3_mux

'define idmux_4_mux3

'define idmux_5_mux3

```

Synthesizing the source codes with the macro definition file, proper resources are chosen to build the application specific processor.

## 3.5 Experimental Result

## 3.5.1 Application Programs

In order to evaluate the effect of the processor adaptation, we evaluated three applications, the matrix multiplication, Rijndael and quick sort program. Features of these applications

Figure 3.6: Example of selecting multiplexer (Adapted).

are as follows.

#### • Matrix multiplication

In Matrix multiplication program, the size of matrices is relatively small,  $4 \times 4$  since the instruction set is not varied if the size of matrices is increased. The initial data of the matrices are stored in Read only area, the address of which is shown in Fig.3.1 and the result of multiplication is stored in RAM for data area. This program uses the multiplier. The actually used data of the matrices are shown below.

$$\begin{pmatrix} 1 & 2 & 3 & 4 \\ 5 & 6 & 7 & 8 \\ 9 & 10 & 11 & 12 \\ 13 & 14 & 15 & 16 \end{pmatrix} \begin{pmatrix} 5 & 6 & 7 & 8 \\ 9 & 10 & 11 & 12 \\ 13 & 14 & 15 & 16 \\ 17 & 18 & 19 & 20 \end{pmatrix} = \begin{pmatrix} 130 & 140 & 150 & 160 \\ 306 & 332 & 358 & 384 \\ 482 & 524 & 566 & 608 \\ 658 & 716 & 774 & 832 \end{pmatrix}$$

(3.1)

#### • Rijndael

Rijndael in Ref. [62] is a cypher algorithm which is commonly used as AES. In this program, an encrypted data is stored in a Read Only Data area so that around 2.8K-byte Read Only Data area is used for a table data which is used in the algorithm. We confirmed the target data was properly decrypted with this algorithm.

#### • Quick sort

Quick sort is a popular algorithm of sorting. In this evaluation, one hundred of integer data are stored in Read Only Data area and the result is stored in RAM for data area and is output with the UART interface on an evaluation board to confirm correctness of the result. The application program from Ref. [63] is used.

Table 3.2: Processor core resources.

| Resource   | Matrix        | Rijndael[62]  | Qsort[63]     | Full          |

|------------|---------------|---------------|---------------|---------------|

| LUT        | 3954(19.01%)  | 3697(17.77%)  | 3835(18.44%)  | 8481(40.77%)  |

| LUTRAM     | 1536(16.00%)  | 1536(16.00%)  | 1536(16.00%)  | 1536(16.00%)  |

| FF         | 1765(4.24%)   | 1701(4.09%)   | 1695(4.07%)   | 1766(4.25%)   |

| BRAM       | 11.50(23.00%) | 11.50(23.00%) | 11.50(23.00%) | 11.50(23.00%) |

| DSP        | 4(4.44%)      | _             | _             | 8(8.89%)      |

| WNS (ns)   | 0.333         | 0.298         | 0.345         | -0.205        |

| Fmax (MHz) | 69.575        | 69.406        | 69.634        | 67.065        |

| Power (W)  | 0.238         | 0.223         | 0.226         | 0.34          |

#### 3.5.2 Evaluation of Processor Adaptation

We evaluated the effect of the processor adaptation. Xilinx Artix-7 FPGA (XC7A35T-ICPG236C) in Ref. [64] on the BASYS3 board of Digilent in Ref. [60] and the Xlinx development tool Vivado 2018.3 are used for the evaluation. GCC 4.3.3 is used for the compiler. For application programs described in Section 3.5.1, FPGA resources which each adaptive processor uses are shown in Table 3.2. Full is a processor core which is not adapted to an application program. The clock rate of the processor (CLK) is 68.0MHz, which is generated by the IP core from the source clock rate of 100MHz. WNS stands for Worst Negative Slack and Fmax is calculated by Fmax = 1000/((1000/(1000/CLK) - WNS)) in Ref. [65]. Power is Total On Chip Power, which is estimated by a Xilinx design tool, Vivado in Ref. [66].

From Table 3.2, it can be seen that the number of LUT resources are reduced by 56.4% (Rijndael) to 53.4% (Matrix) from the full set of the processor (Full) and Fmax is higher than 68.0MHz for the adapted cases while the timing is not met in the Full, not adapted case.

#### 3.5.3 Discussion

Table 3.3 shows the resource usage of Qsort[63] to see the effect of the adaptation in detail. The column "Adapted" is cited from Table 3.2 for the case of adaptation applied. The column "w/ Multi." is the case of "Adapted" with additional resources for multiplication. The column "w/ Div. signed" is the case of "Adapted" with additional resources for signed division as we can select the signed division and/or the unsigned division for the resources of division. The column "w/o load half word" shows the resources of the case that load half word instruction related resources are removed from "No Adaptation" as in the Fig.3.6. It can be seen that about 0.3% of LUT can be reduced by the removing load half word related resources. We can also see that 3.6% and 62.6% of LUT are increased with multiplier and signed divisor, respectively.

Table 3.3: Processor core resources in detail (Qsort[63]).

| Resource            | Adapted | w/ Multi. | w/ Div. | w/o load  | No Adaptation |

|---------------------|---------|-----------|---------|-----------|---------------|

|                     |         | ,         | signed  | half word | •             |

| LUT                 | 3835    | 3972      | 6235    | 8459      | 8486          |

| LUTRAM              | 1536    | 1536      | 1536    | 1536      | 1536          |

| $\operatorname{FF}$ | 1695    | 1765      | 1767    | 1765      | 1766          |

| BRAM                | 11.50   | 11.50     | 11.50   | 11.50     | 11.50         |

| DSP                 | _       | 8         | _       | 8         | 8             |