## **JAIST Repository**

https://dspace.jaist.ac.jp/

| Title        | [課題研究報告書]グラフニューラルネットワークの実装技術に関する調査     |

|--------------|----------------------------------------|

| Author(s)    | 玉川, 徹                                  |

| Citation     |                                        |

| Issue Date   | 2024-09                                |

| Туре         | Thesis or Dissertation                 |

| Text version | author                                 |

| URL          | http://hdl.handle.net/10119/19369      |

| Rights       |                                        |

| Description  | Supervisor: 田中 清史, 先端科学技術研究科, 修士(情報科学) |

## 課題研究報告書

## グラフニューラルネットワークの 実装技術に関する調査

玉川徹

主指導教員 田中清史

北陸先端科学技術大学院大学 先端科学技術研究科 (情報科学)

令和6年9月

## 概要

ソーシャルネットワークを始めグラフ構造で表現可能な様々な関係に対して、クラス分類/回帰問題等を扱うグラフニューラルネットワーク (GNN) およびグラフ畳み込みニューラルネットワーク (GCN) が注目されている. ハードウェア実装して推論/トレーニングの速度を改善したり、消費電力の削減をするためには、入力として与えられるグラフを行列形式で表現した際に、非ゼロの要素のデータ分布が非常にアンバランスである点、および、行列サイズが非常に大きい点を考慮した設計をする必要がある. GNN / GCN の要素技術についてこれまで数々の研究がなされてきたが、GNN / GCN のハードウェア実装に関する知識の整理が不完全であるという課題がある. 本研究では、GNN / GCN のハードウェア実装に特に注目して、関連するこれまでの研究について、分類および有効な最適化手法を明らかにすることにより知識の整理を行った.

GNN / GCN のハードウェア実装は、推論レイテンシの削減、消費電力の削減、 メモリアクセスの効率化等, 様々な最適化目標を持っている. また, 対象とする GNN の処理フェーズやデータセット, ネットワーク等, 前提とする条件も論文によ り大きく異なる.既存研究におけるこれらの実装の傾向を明らかにするために,各 手法において対象とするフェーズ, 目的, データセット, ネットワーク, デバイス, お よび量子化精度に基づいて整理した. GNN / GCN のハードウェア実装の対象フ ェーズは, ①推論(推論のみに対応), ②トレーニング(トレーニングのみに対応), ③推論とトレーニング (推論とトレーニングの両方に対応) の3種類に分類される. ハードウェア実装の全体的な傾向として,フェーズについては,推論フェーズのみ を対象とする論文が75本、トレーニングフェーズのみを対象とする論文が20本、 推論/トレーニングの両方のフェーズを対象とする論文が5本であり,推論フェー ズを対象とする論文数が非常に多い. これは,推論は訓練済みモデルを実際のアプ リケーションで使用する段階であり,多くの実際のアプリケーションで実行するに あたって低遅延の処理が求められていて,推論の高速化に対する需要がトレーニン グと比べて高いことが要因として考えられる. 目的については, 大半の研究がレイ テンシと消費電力の削減の2つを挙げているが,他にも,オフチップメモリアクセ スの削減やチップ面積の削減,オフチップメモリ帯域幅使用量の削減を目的とする 既存研究もある. データセットについて, ①推論の対象データセットでは, 上位4つ の Cora, Reddit, Citeseer, Pubmed を対象としている論文は 40 本以上ありこれらが 大半を占めていた. ②トレーニングのみを対象とするハードウェア実装について

は、①と同様 Reddit と、Yelp、OGBN-products、Amazon が上位 4 つであった。③推論 /トレーニングの両方を対象とするハードウェア実装についても、Reddit、Cora、 Citeseer、Pubmed 等、① / ②と同様のデータセットが採用されている。ネットワークについては GCN が極めて多く採用さていて、デバイスについては大半が ASIC あるいは FPGA である。量子化精度については、論文中で明示されていないものの中では特徴ベクトル/重みベクトルにおいて 32bit 固定小数点 / 32bit 浮動小数点 が多く採用されている.

# 目次

| 第1章 | はじ  | めに                       | 8  |

|-----|-----|--------------------------|----|

| 第2章 | 背景  |                          | 11 |

| 2.  | .1  | GNN / GCN の実世界のアプリケーション例 | 11 |

| 2.  | .2  | GNN / GCN の基本概念と定義       | 12 |

| 2.  | .3  | GNN / GCN の実行プラットフォームの概要 | 17 |

| 第3章 | GNN | N / GCN アクセラレーションの分類     | 21 |

| 3.  | .1  | 分類項目の定義                  | 21 |

| 3.  | .2  | 分類表と考察                   | 21 |

| 第4章 | 最適  | 化手法                      | 41 |

| 4.  | .1  | HyGCN                    | 41 |

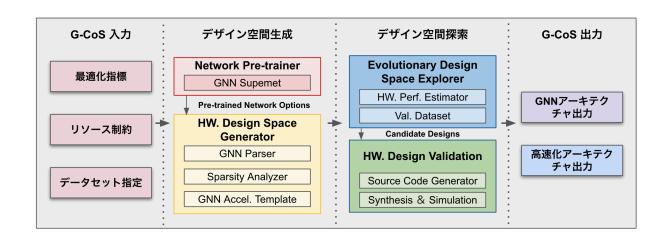

| 4.  | .2  | G-CoS                    | 43 |

| 第5章 | タス  | クスケジューリング                | 46 |

| 5.  | .1  | AWB-GCN                  | 46 |

| 5.  | .2  | EnGN                     | 48 |

| 第6章 | 今後  | の課題と展望                   | 51 |

| 第7章 | おわ  | りに                       | 55 |

## 図目次

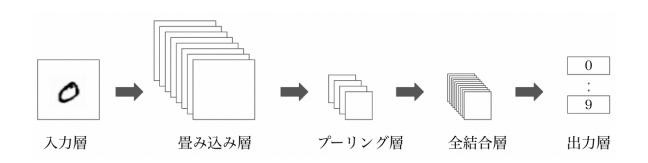

| 1  | CNN の全体像の簡易図                          | 12 |

|----|---------------------------------------|----|

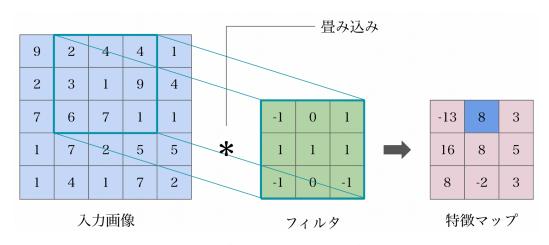

| 2  | 入力画像から特徴マップの生成                        | 12 |

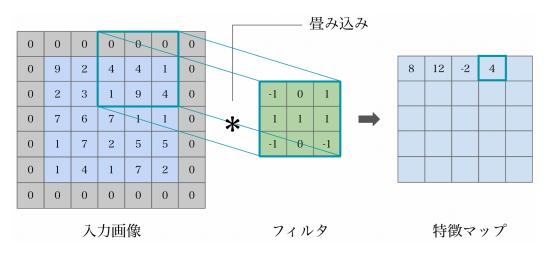

| 3  | ゼロパディング                               | 13 |

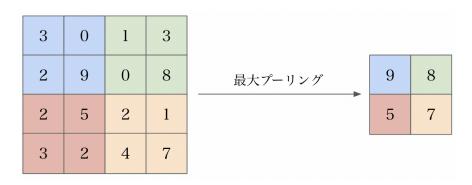

| 4  | 最大プーリング                               | 13 |

| 5  | 平均プーリング                               | 14 |

| 6  | GNN の推論の流れ [33]                       | 15 |

| 7  | GNN のトレーニングの流れ [33]                   | 15 |

| 8  | 各ハードウェアアーキテクチャの比較 [37]                | 18 |

| 9  | CPU と GPU の比較 [38]                    | 19 |

| 10 | 推論のみを対象とする GNN / GCN ハードウェア実装のデータセ    |    |

|    | ット毎の論文数                               | 23 |

| 11 | トレーニングのみを対象とする GNN / GCN ハードウェア実装の    |    |

|    | データセット毎の論文数                           | 24 |

| 12 | 推論/トレーニングの両方を対象とする GNN / GCN ハードウェ    |    |

|    | ア実装のデータセット毎の論文数                       | 25 |

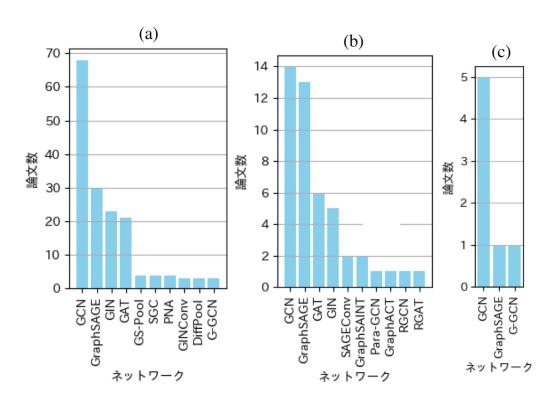

| 13 | GNN / GCN ハードウェア実装のネットワーク毎の論文数 (a) 推論 |    |

|    | が対象 (b) トレーニングが対象 (c) 推論/トレーニングの両方が対象 | 26 |

| 14 | GNN / GCN ハードウェア実装のデバイス毎の論文数 (a) 推論が対 |    |

|    | 象 (b) トレーニングが対象 (c) 推論/トレーニングの両方が対象   | 26 |

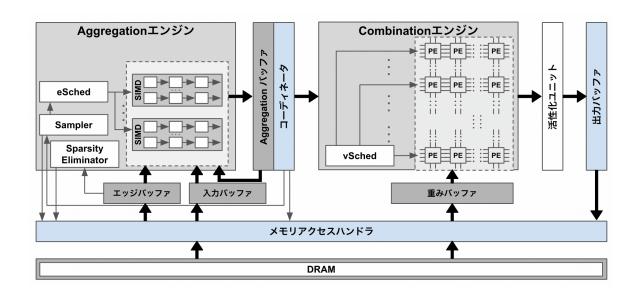

| 15 | HyGCN のアーキテクチャの概要 [9]                 | 41 |

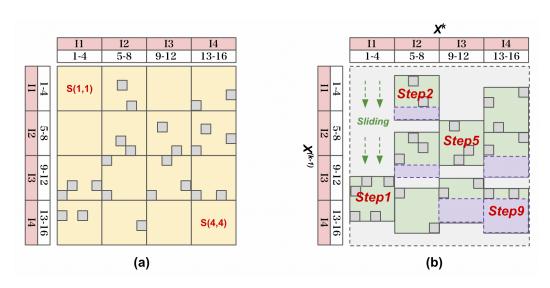

| 16 | (a) データの局所性向上のための静的なグラフ分割 (b) スパース性除  |    |

|    | 去のための Sliding Window アプローチ            | 41 |

| 17 | G-CoS フレームワークの概要 [49]                 | 43 |

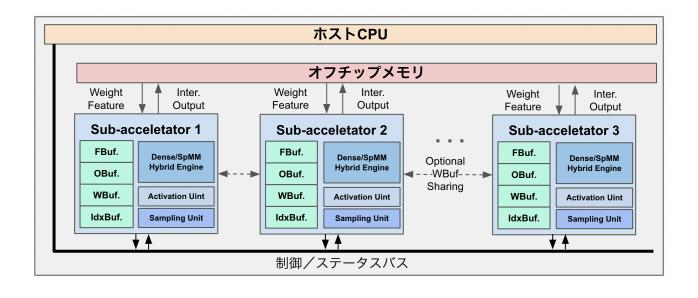

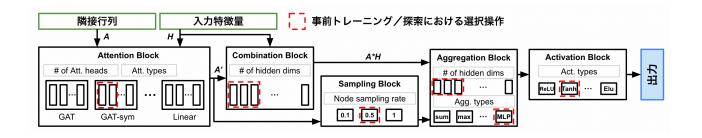

| 18 | G-CoS マイクロアーキテクチャ・テンプレートの概要 [49]. 入力と                   |    |

|----|---------------------------------------------------------|----|

|    | して与えた制約条件と, GNN のアーキテクチャに応じてサブアクセ                       |    |

|    | ラレータの数やバッファの容量が異なる                                      | 43 |

| 19 | G-CoS の GNN スーパーネットのセグメント [49]                          | 44 |

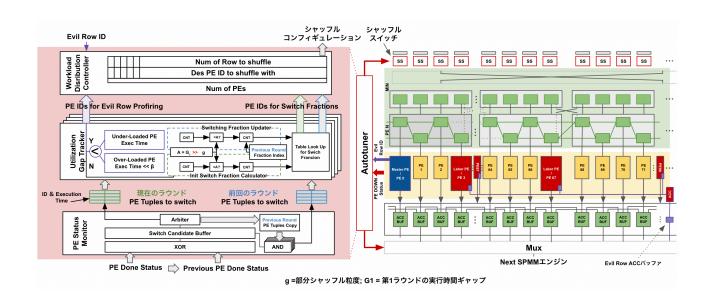

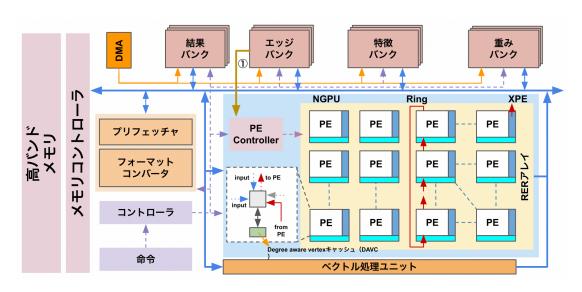

| 20 | AWB-GCN アーキテクチャの概要 [10]                                 | 46 |

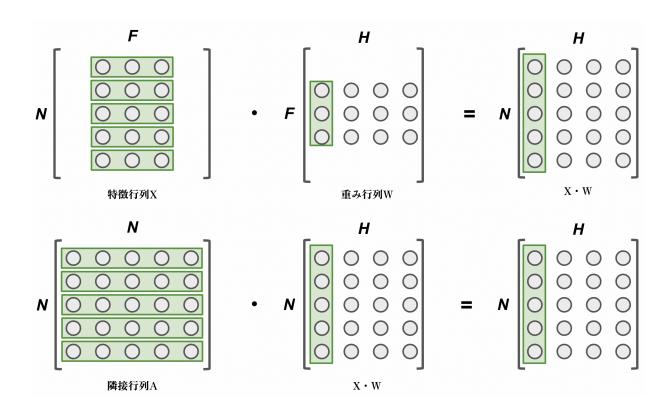

| 21 | 1 ラウンドで $N 	imes H$ の出力行列の $1$ 列の結果が算出されることを表           |    |

|    | す図. N はグラフのノード数, F は入力特徴量の次元数, H は出力特                   |    |

|    | 徴量の次元数を表す                                               | 47 |

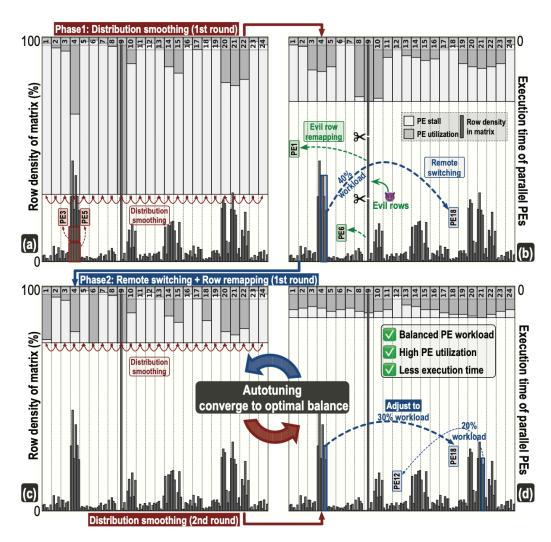

| 22 | 負荷分散の流れ([10] から転載. ©2020 IEEE.). 計算フェーズで                |    |

|    | Distribution smoothing を実行後, 負荷分散フェーズで Remote switching |    |

|    | と Row remapping を実行する                                   | 48 |

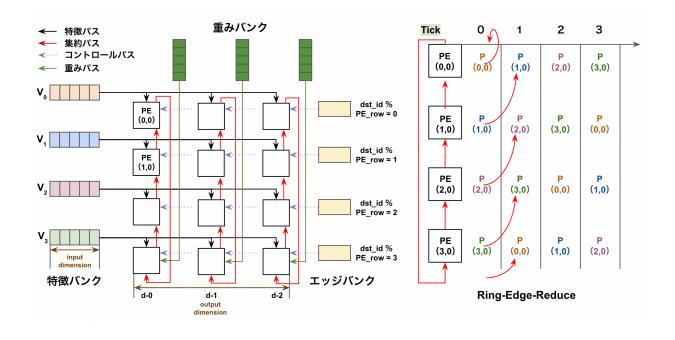

| 23 | EnGN のアーキテクチャの概要 [39]                                   | 49 |

| 24 | Ring-Edge-Reduce の仕組み [39]                              | 49 |

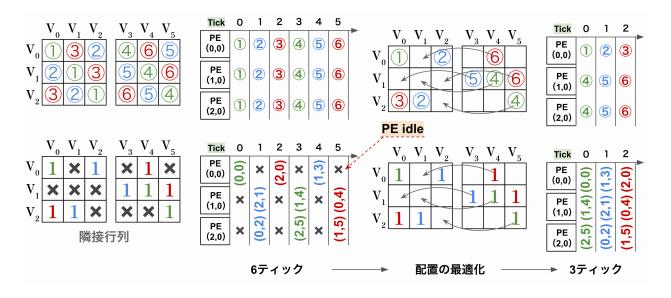

| 25 | エッジの並び替え [39]                                           | 50 |

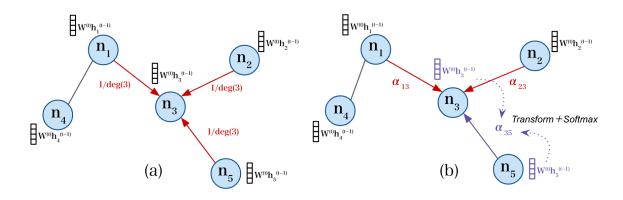

| 26 | GCN における集約処理 (a) と GAT における集約処理 (b) の比較.                |    |

|    | GCN における集約処理では, 各ノードは隣接するノードから情報が                       |    |

|    | 重み付き和で集約される. 重みは隣接ノードの次数に基づいて決定                         |    |

|    | され, 具体的には各重みは $\frac{1}{\deg(i)}$ となる. GAT ではアテンション係数   |    |

|    | $a_{ij}$ を使って集約される。アテンション機構により,異なる隣接ノー                  |    |

|    | ドに対して異なる重要度を割り当てることができる. GAT は GCN                      |    |

|    | に比べて表現力と柔軟性が増す一方で, 計算の複雑さが増す                            | 51 |

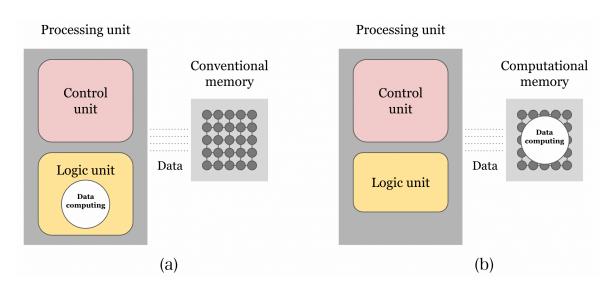

| 27 | (a) ノイマン型アーキテクチャと (b) インメモリ型の比較. ノイマン                   |    |

|    | 型アーキテクチャでは CPU とメモリが分離していて, CPU がメモリ                    |    |

|    | から命令を取り出して実行して結果をメモリ等の記憶装置に格納す                          |    |

|    | る処理を逐次的に行う. これに対してインメモリ型では, メモリチッ                       |    |

|    | プ内に計算回路が組み込まれていて, CPU とメモリ間のオーバーへ                       |    |

|    | ッドがない状態で命令を実行していくことができる                                 | 52 |

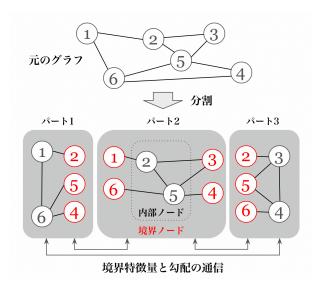

| 28 | PipeGCN の分散トレーニングの仕組み [11]. 元のグラフを複数のグ                  |    |

|    | ラフに分割して, 複数のパートをそれぞれ異なる GPU にアサインし                      |    |

|    | てトレーニングを行う                                              | 53 |

|    |                                                         |    |

# 表目次

| 1 | GCN アルゴリズムに関する表記と説明 [33]                | 16 |

|---|-----------------------------------------|----|

| 2 | GNN の派生形 [33]                           | 17 |

| 3 | GNN / GCN のハードウェア実装で用いられる代表的なベンチマー      |    |

|   | ク用データセット. クラスは, データセット内の分類のカテゴリを表       |    |

|   | す. 例えば Cora の場合, 強化学習, ニューラルネットワーク, 事例べ |    |

|   | ース,遺伝的アルゴリズム,確率的手法,ルール学習,理論という7つ        |    |

|   | の論文カテゴリが存在することを意味する. 特徴量は, 各ノードに        |    |

|   | 対して付与されていて, ノードの特徴を表す. 例えば Cora の場合, 特  |    |

|   | 徴量は論文要旨の単語の集合を表していて, 使用される語彙の数は         |    |

|   | 1,433 である                               | 22 |

| 4 | 推論のみを対象とする GNN / GCN ハードウェア実装の既存研究      |    |

|   | の分類                                     | 28 |

| 5 | トレーニングのみを対象とする GNN / GCN ハードウェア実装の      |    |

|   | 既存研究の分類                                 | 37 |

| 6 | 推論/トレーニング両方を対象とする GNN / GCN ハードウェア      |    |

|   | 実装の既存研究の分類                              | 40 |

## 第1章 はじめに

ソーシャルネットワークを始めグラフ構造で表現可能な様々な関係に対して、クラス分類/回帰問題等を扱うグラフニューラルネットワーク(GNN)[1] およびグラフ畳み込みニューラルネットワーク(GCN)[2] が注目されており、その推論速度と電力効率の改善のために様々な取り組みがされている。これらをハードウェア実装により推論/トレーニングの速度を改善したり、消費電力の削減をするためには、入力として与えられるグラフを行列形式で表現した際に、①非ゼロの要素のデータ分布が非常にアンバランスである点、および、②行列サイズが非常に大きい点を考慮した設計をする必要がある。従来のニューラルネットワークの行列乗算に適している GPU は、多数のスレッドを並列に実行できるアーキテクチャを持ち、大規模な行列演算において優れた性能を発揮するが、主に密な行列演算に最適化されているためスパース行列の非ゼロ要素の不均一な分布に対しては処理効率が低下する。また CPU は、そもそも大規模な行列演算に適したアーキテクチャではない。したがって、従来の汎用的なハードウェアアーキテクチャはグラフ構造を効率よく処理するためには適していないため、それらをハイブリッドで実行するための仕組みを構築したり、FPGA や ASIC で実装する等、専用の最適化が不可欠である。

非ゼロのデータ分布がアンバランスである場合,特定の演算ユニットに対して過剰な負荷がかかる一方で,他の演算ユニットがアイドル状態になることがある.これは,現実世界の様々な関係をグラフ構造で表現した際に,非ゼロの要素が特定の領域に集中し,他の領域がほとんど空であるということが頻繁に発生することに起因する.結果として,全体としての計算効率が低下しリソースの無駄が生じることに加え,アイドル状態の演算ユニットが増えることに伴いエネルギー効率も低下し,無駄な電力消費が発生する.この課題は特にスパース行列の操作において顕著であり,効率的な計算処理を妨げる大きな要因となる.この問題を解決するためには,負荷状況に基づいて動的にタスクの割り当て先の演算ユニットを切り替えたり,推論/トレーニングを開始する前にグラフ特性を考慮したグラフの並び替えを行うことで,各演算ユニットに均等に処理を分配するといった設計上の工夫を行うことが重要である.また,非ゼロの要素の位置情報を効率的に管理するために効率的なデータ圧縮技法を検討することも有効な対策となりうる.

非常に大きな行列サイズに対処するためには, 大規模なデータを効率的に処理できるハードウェアアーキテクチャが求められる. これを実現するにあたって, まず

メモリ階層の最適化が必要である. 大規模な行列データを効率的に取り扱うためには、オンチップメモリとオフチップメモリの両方を効果的に活用することが求められる. オンチップメモリを利用して頻繁にアクセスされるデータの局所性を高め、オフチップメモリへのアクセスを最小限に抑えることで、メモリ帯域幅の制約を克服し全体のスループットを向上させることができる. また、並列処理能力の向上も欠かせない要素である. 大規模な行列計算を効率的に行うためには、多数の演算ユニットを並列に協調動作させるアーキテクチャを採用することで、計算効率を大幅に向上させることができる. さらに、データの局所性を最大限に活用するためのキャッシュ階層の最適化や、データの再利用を促進するためのバッファ管理も重要な要素となる. これらのアプローチにより、メモリアクセスのオーバーヘッドを削減し、計算処理のスループットを向上させることが可能となる.

GNN / GCN のハードウェア実装の既存研究について, HyGCN[9] では, GCN の 推論処理が集約と結合という,2つの性質の異なるフェーズで構成されることに着 目して、それぞれのフェーズに特化したモジュールを持つハイブリッド・アーキ テクチャを提案している. AWB-GCN[10] では, 入力データである隣接行列につい て, 非ゼロの要素が極めて多くかつ不均一に存在するため, 不要なゼロ乗算が多く 発生して計算効率が悪化するという問題に対応するために, 各演算ユニットに割 り当てる負荷を分散するための自動チューニング技術を提案している. I-GCN[11] では,推論処理における行列乗算を行うにあたってデータの局所性を高めるため に, 隣接行列のデータを複数の L 字型クラスタに並び替える手法を提案している. PipeGCN[12] では, GCN データセットをサブグラフに分割して複数の GPU に割り 当てて、それぞれでトレーニングを実行する分散 GCN トレーニングという手法の 通信コストを改善することで,トレーニングの速度を改善する手法を提案してい る. また COIN[13] では, アナログ回路をメモリ上に実装することでインメモリ・ア クセラレータを実現して,推論速度や消費電力の改善をするための手法を提案して いる. 多くの論文が推論/トレーニングの実行時間の短縮や消費電力の削減を目 的としてハードウェア実装の手法を提案しているが、それらを実現するためのアー キテクチャは多種多様である.

GNN / GCN の要素技術についてこれまで数々の研究がなされてきたが、GNN / GCN のハードウェア実装に関する知識の整理が不完全であるという課題がある. 要因として、①新しい手法が頻繁に提案されている研究領域であること、②入力として与えるグラフやネットワーク構造、ハードウェアデバイス種別等、何らかの

制約条件に特化した手法が多数存在するため、手法間で条件を揃えた状態で性能比較することが容易ではないこと、③論文の手法を再現するために必要なハードウェアを揃えたり、不足している技術的な詳細情報について検討した上で実装するコストが大きいこと、等が考えられる.以上の要因により、対象問題/用途に対してどのようなネットワーク構成/システム構成が相応しいのかが不明瞭であるのが現状である.

本研究では、GNN / GCN のハードウェア実装に特に注目して、関連するこれまでの研究について、分類および性能との関係を明らかにすることにより GNN / GCN 分野の知識の整理の一助となる点で重要性がある。これにより、①従来の手法によって解決していない問題の顕在化、②GCN ハードウェア実装の知識を習得したい初学者の学習効率化に貢献することを目指す。

本論文の構成は、第2章でGNN/GCNのアプリケーション例や、GNN/GCNの概要、GNN/GCNの実行プラットフォームについて論じた後、第3章では既存研究のGNN/GCNアクセラレータの分類を行う。そして第4章では、特徴的な最適化手法/スケジューリングを提案しているものをいくつか紹介して、第5章の今後の課題と展望では現状のアクセラレータ群で解決されていない事柄について示す。

## 第2章 背景

#### 2.1 GNN / GCN の実世界のアプリケーション例

GNN / GCN は,グラフ構造という汎用的なデータ構造を取り扱うネットワークであり,多くの現実世界の関係を表現することができるため,実社会での応用範囲が非常に広く,今後適用される領域はさらに広がっていくことが予想される.本節では,GNN / GCN の様々な適用・応用例を示す.

ソーシャル領域について、SocialGCN[14]、MSGCN[15]では、ユーザーの過去の行動履歴(レビューや「いいね」等)と、ユーザー間のソーシャルネットワーク構造(フォロー関係等)を活用して、ユーザーが好むと予測されるコンテンツ(店舗、画像、他の利用ユーザー等)を推薦する手法を提案している。CayleyNets[16]、GUCD[17]では、電力網運用において、ソーシャルネットワーク等のグラフ構造における共通の趣味や属性を持つノードの集合を発見するための手法を提案している。NESA[18]、DTGRU[19]では、ソーシャルネットワークの世論識別等を目的として各テキストの感情分析をするためにGCNを適用している。また、M-GCN[20]、KMGCN[21]、KMAGCN[22]では、フェイクニュースの検出のためにGCNが活用されている。

交通領域について、ASTGCN[23]、T-MGCN[24] では、道路網の交通状況の空間的依存関係、時間的依存関係等をもとに交通流予測をするための手法を提案している。この手法は、渋滞の予測、事故リスクの予測、公共交通機関/タクシーの運行管理等への応用が想定される。

電力インフラ領域について、GCMCN[24]では、風力発電において、風速、風向といった空間的特徴量と、時間的特徴量(時系列データ)を同時に考慮した風力発電量の予測手法を提案している。Kim 他 [26] は、送電線が不測の事態で過負荷になるのを防ぐための最適な負荷遮断比を予測する手法を示している。

創薬領域について、Decagon[27]では、多数の種類の薬剤を同時併用することによる副作用のリスクが臨床試験で見逃されやすく予測が難しいという課題を解決するために、副作用予測をするための手法を提案している。Ma他 [28]では、薬物間の類似性を予測するために、化学構造、薬物間相互作用、副作用等、様々なドメインから得られる薬物の情報をもとにグラフ構造を構築してトレーニングして、解釈性の高い予測モデルを構築している。Gao他 [29]では、ある薬物分子の化学構造式と

タンパク質のアミノ酸配列を入力として、その組み合わせが結合する可能性が高いかどうかを予測する手法を提案している.

金融領域について、SemiGNN[30]、TA-Struc2Vec[31]では、ユーザー間の関係性や属性情報等を統合して、グラフ構造に基づいた金融詐欺の検出をするための手法を提案している。

以上のように、グラフデータを扱う技術の進化と共に GNN / GCN の適用領域は今後さらに広がっていき、様々な産業や研究分野における新しい応用が次々と登場することが期待される.

#### 2.2 GNN / GCN の基本概念と定義

図 1: CNN の全体像の簡易図

GNN は, CNN[32] における畳み込み演算を非構造グラフデータに適用できるように一般化したものである.

図2: 入力画像から特徴マップの生成

前提として, CNN は主に画像認識や画像解析の分野で活用されるディープラーニングのアルゴリズムで, 画像データから特徴を抽出し, 分類や検出等のタス

図 3: ゼロパディング

図 4: 最大プーリング

クを行う用途で用いられる. CNN は主に5つの層(入力層, 畳み込み層, プーリング層, 全結合層, 出力層)で構成される(図 1). 入力層では, 画像データがピクセル値としてネットワークに与えらえる. 畳み込み層では, フィルタ(カーネル)を用いて入力データに対してフィルタのウィンドウを一定の間隔(ストライド)でスライドさせながら, フィルタの要素と入力データの対応する要素を乗算してそれらの和を求め(積和演算), 出力結果の対応する場所(左上から順)に格納する. 図 2 において, 特徴マップの青背景上の 8 は以下のように計算される: 8 = 2×-1+4×0+4×1+3×1+1×1+9×1+6×-1+7×0+1×-1. 畳み込み演算の結果として, 入力画像から特徴マップが生成され, 画像の局所的な特徴が強調される. ただし, 畳み込みを行うとカーネルが入力の端まで到達できないことに伴い画像のサイズが徐々に小さくなり, 入力の端に近い情報が失われる. これを防ぐためにパディング(図 3)という手法により入力画像のピクセルの周りにピクセルを囲むことで, 入力の端の情報を保持しながら、畳み込み演算を適用する. 次にプーリング層では, 特徴マップのサイズの縮小を行なうことで全結合層で必要な計

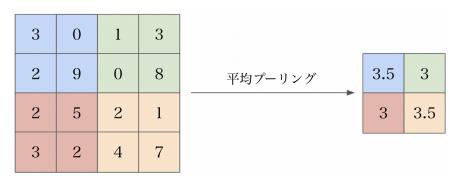

図 5: 平均プーリング

算量の削減を行う. 一般的なプーリング手法としては,最大プーリング(図4)や平均プーリング(図5)がある. 最大プーリングでは領域内で最も大きな値が選択され,平均プーリングでは,領域内のピクセル値の平均値が算出される. これらにより,特徴マップの重要な情報を保持しつつ,データのサイズが圧縮される. 続いて全結合層で特徴マップによって得られたそれぞれの特徴量を1つのノードに集約を行った後,出力層において活性化関数を適用することで最終的な結果が得られる.

CNN は,主に画像データの処理に優れているが,いくつかの問題点がある.まず, CNN は規則的なグリッド状のデータ(画像等)に適しているが, グラフのような 多次元構造には適していない. 画像データは, ピクセルが規則的に配置された 2 次 元のグリッド構造を持っていて, CNN は, このような規則的な構造を活かして局所 的な特徴を効率的に抽出することができる. 畳み込み層では, フィルタを用いて画 像の局所的な特徴を抽出し, プーリング層では, 特徴量を圧縮・要約することで画 像の重要な特徴を効果的に抽出する.しかし、グラフデータは多次元の構造を持ち ノード間の関係性が複雑であるため, CNN のような規則的なグリッド構造に基づ く処理には適していない.グラフデータでは、ノード数や接続関係が一定ではなく、 ノード間の距離も一様ではない. さらに, グラフデータにはノードの順序に意味が ないという性質, つまり, ノードの並び方を変えてもグラフの構造や意味が変わら ないという性質がある. 例えば、ソーシャルネットワークのグラフで、ユーザーAと ユーザーBが友人関係にあるとき、「AとBが友人である」ことと「BとAが友人 である」ことは同じ意味を持つ. この性質に伴い, グラフデータを扱う際にはノー ドの順序を考慮する必要がない. しかし, CNN は入力データの空間的な配置を考慮 して特徴量を学習するため、ノードの順序に意味がないグラフデータでは CNN で 生成する特徴量が意味を持たない. また, CNN は固定サイズの入力を想定している ため,ノード数が可変であるグラフデータを直接扱うことは難しい.このように,グ ラフデータの持つ多次元構造,ノード数や接続関係の可変性,ノードの順序に意味がないという性質により,CNN をグラフデータに直接適用することは困難である.

CNN の課題を解決するために, グラフ構造を直接扱うことのできるニューラルネットワークとして, GNN が提案された. GNN では, 各ノードの特徴量を更新する際に隣接するノードの情報を集約することで, グラフ構造に応じた柔軟な特徴量の更新が可能になる.

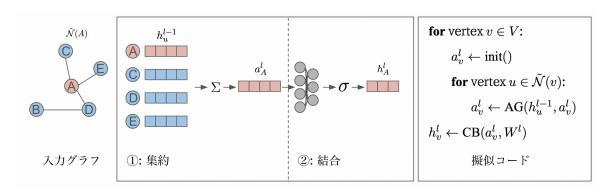

図 6: GNN の推論の流れ [33]

図 7: GNN のトレーニングの流れ [33]

一般に、GNN モデルは入力グラフ G = (V, E) が与えられたとき (V & E) は頂点 と辺の集合である)、以下のように抽象化される 2 段階の演算(式 1: 集約、式 2: 結合)を行う.

$$a_v^l = \text{AGGREGATE}\left(h_u^{l-1} \mid u \in \tilde{\mathcal{N}}(v)\right)$$

(1)

$$h_v^l = \text{COMBINE}(a_v^l) \tag{2}$$

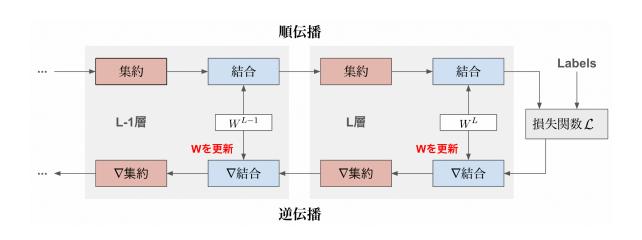

GNN の推論では,順伝播の計算を畳み込み演算として行う.順伝播は,ノードの特徴量を隣接ノードの特徴量から集約,結合することでノードの新しい特徴量を計算するプロセスである(図 6). GNN のトレーニングでは,順伝播の計算,損失計算,逆伝播の計算,重みの更新をモデルが収束するまで行う(図 7).

表 1. GCN アルゴリズムに関する表記と説明 [33]

| 表記                                          | 説明                                                             |

|---------------------------------------------|----------------------------------------------------------------|

| $\overline{V,E}$                            | ノードとエッジの集合                                                     |

| $\mathcal{N}(v)$                            | ノード v の隣接ノードの集合                                                |

| $\tilde{\mathcal{N}}(v)$                    | $v$ と $v$ の隣接ノードを含む集合: $\{\mathcal{N}(v)\} \cup \{v\}$         |

| $D_v$                                       | ノード $v$ の次数                                                    |

| L                                           | モデルの総レイヤー数                                                     |

| $h_v^l$                                     | 第 $l$ 層のノード $v$ の隠れ特徴ベクトル                                      |

| $egin{aligned} d_v^l \ a_v^l \end{aligned}$ | 第 l 層の隠れ特徴ベクトルの次元                                              |

| $a_v^l$                                     | 第 $l$ 層のノード $v$ の集約された特徴ベクトル                                   |

| $W^l$                                       | 第 $l$ 層の重みベクトル                                                 |

| $z_v^l$                                     | 活性化関数適用前の特徴ベクトル, すなわち $a_v^l \cdot W^l$                        |

| $\sigma$                                    | 活性化関数,例: ReLU                                                  |

| ${\cal L}$                                  | 出力とラベルを用いて計算された損失値                                             |

| $\delta_v^l$                                | $h_v^l$ の勾配, すなわち $rac{\partial \mathcal{L}}{\partial h_v^l}$ |

| $\hat{\delta}_v^l$                          | $h^l_v$ のマスクされた勾配: $\delta^l_v \odot \sigma'(z^l_v)$           |

| $\hat{\delta}_v^{'l}$                       | ノード v の集約・マスク済勾配                                               |

GNN は,グラフ構造データを扱うニューラルネットワークの総称で,様々なアーキテクチャが存在するが,その中でも代表的なものの1つがGCNである.GCNでは,入力グラフの各頂点に自己ループを追加することで,隣接ノードだけでなく自身のノードも計算に加える実装になっている.GCNのアルゴリズムの議論で使用する表記を表1に示す.

具体的な計算について、まず集約フェーズ(式 3)では、各ノードvに対して、その隣接ノードの特徴量  $h_u^{l-1}$  を集約する. 結合フェーズ(式 4)では、集約された特徴  $a_v^l$  に対して、重み行列  $W^l$  を適用し、活性化関数  $\sigma$  を通して新しいノード特徴  $h_v^l$  を計算する.

$$a_v^l = \sum_{u \in \tilde{\mathcal{N}}(v)} \frac{1}{\sqrt{D_v D_u}} h_u^{l-1} \tag{3}$$

$$h_v^l = \sigma(a_v^l \cdot W^l) \tag{4}$$

次に, 損失計算について, GCN の代表的なタスクであるノード分類では交差エントロピー誤差を適用する(式5).

正解ラベルとの誤差を算出

$$\mathcal{L} = \frac{1}{N} \sum_{v=1}^{N} CrossEntropyLoss(h_v^L, y_v)$$

(5)

さらに, 逆伝播の計算(式6)で, 重みの勾配を計算する.

$$\frac{\partial \mathcal{L}}{\partial W^{l}} = \sum_{v=1}^{N} \frac{\partial z_{v}^{l}}{\partial W^{l}} \cdot \frac{\partial \mathcal{L}}{\partial z_{v}^{l}} = \sum_{v=1}^{N} a_{v}^{l} \cdot \frac{\partial \mathcal{L}}{\partial h_{v}^{l}} \cdot \frac{\partial h_{v}^{l}}{\partial z_{v}^{l}}$$

$$= \sum_{v=1}^{N} a_{v}^{l} \cdot \delta_{v}^{l} \odot \sigma'(z_{v}^{l}) = \sum_{v=1}^{N} a_{v}^{l} \cdot \hat{\delta}_{v} \tag{6}$$

最後に,重みの更新を行う(式7).

$$W^{l} = W^{l} - \eta \frac{\partial \mathcal{L}}{\partial W^{l}} \tag{7}$$

GNN には GCN 以外にも様々なアーキテクチャがあり, 代表的なものとして, GIN(Graph Isomorphism Network) [34], GraphSAGE(Graph Sample and Aggregation) [35], GAT(Graph Attention Network) [36] が挙げられる. それぞれのアーキテクチャは異なる方法でノード間の情報を集約・結合することで, グラフデータの処理を行う (表 2).

| 派生形          | 集約                                                                                                                                            | 結合                               |

|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|

| GCN[1]       | $a_v^l = \sum_{u \in \mathcal{N}(v)} \frac{1}{\sqrt{D_v D_u}} h_u^{l-1}$                                                                      | $\mathrm{Relu}(a_v^l \cdot W^l)$ |

| GIN[34]      | $a_v^l = (1 + \epsilon) \cdot h_v^l + \sum_{u \in \mathcal{N}(v)} h_u^l$                                                                      | $MLP(a_v^l, W^l, b^l)$           |

| SAGEConv[35] | $a_v^l = \operatorname{Mean}(h_u^l   u \in \mathcal{N}(v))$                                                                                   | $\mathrm{Relu}(a_v^l \cdot W^l)$ |

| GAT[36]      | $\alpha_{vu} = \operatorname{Softmax}(\sigma(a^T[W_1^l h_v^l    W_2^l h_u^l]))$ $a_v^l = \sum_{u \in \mathcal{N}(v)} \alpha_{vu} \cdot h_u^l$ | $\mathrm{Elu}(a_v^l \cdot W^l)$  |

表 2. GNN の派生形 [33]

### 2.3 GNN / GCN の実行プラットフォームの概要

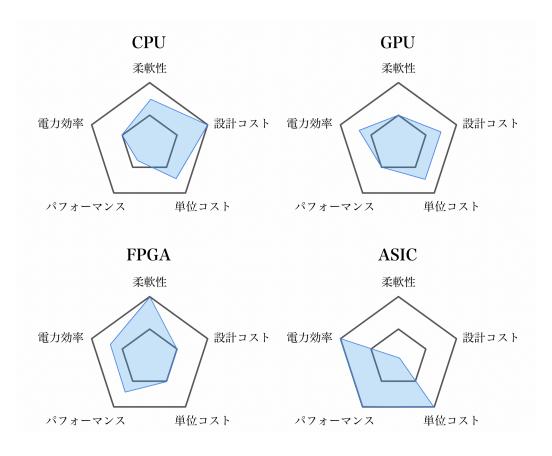

GNN / GCN の実行プラットフォームである, CPU, GPU, FPGA, ASIC のそれぞれのデバイスの特徴, 優位性について示す. 図8では、各ハードウェアアーキテクチ

図 8: 各ハードウェアアーキテクチャの比較 [37]

ャがいくつかのパラメータで評価されている.

- Flexibility (柔軟性):様々なユースケースに対する適応性の高さを表す指標.

- Design Cost (設計コスト): 設計に必要なコストを表す指標.

- Unitary Cost (単位コスト): 完成品1つあたりの製造コスト (量産時のコスト) を表す指標.

- Performance (パフォーマンス):与えられたタスクに対するレイテンシやスループット等を表す指標.

- Power Efficiency (電力効率): 実行に必要な電力を表す指標.

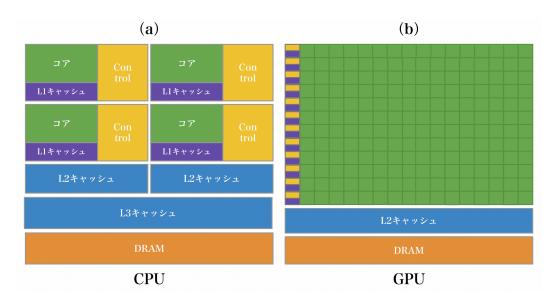

CPU(Central Processing Unit) は,特定のアプリケーションに特化せずに汎用的な用途で使うことを前提に設計された汎用プロセッサである. CPU は図 9(a) のように,主に制御ユニット,コア (ALU: 算術論理演算ユニット), DRAM(Dynamic Random Access Memory),キャッシュにより構成される. CPU は基本的に命令を1つずつ順番に実行するシーケンシャルな処理に最適化されていて,多様なタスクを処理できるよう汎用性を重視して設計されている. プログラミングの容易/柔軟性

図 9: CPU と GPU の比較 [38]

さもあり、最も汎用的なプラットフォームとして広く使われてきた.しかし、ディープラーニングのような大規模な行列乗算のタスクを実行するにあたっては、CPUのコア数は GPU 等と比べて少ないため並列処理を行うにあたってスループットが非常に悪化する. そのため、ディープラーニングの領域では他のアーキテクチャのハードウェアが適用されることが多い.

GPU(Graphics Processing Unit) は,ある程度の柔軟性を維持しながら特定の計算タスク(例えば、3D グラフィックのレンダリング)を改善する用途で設計されたプロセッサである. しかし、ディープラーニングの計算要求と非常に適合していることから、現在では大規模な行列乗算用途でも積極的に使われている. CPU の面積の大半は制御ユニット、キャッシュ、DRAM が大部分を占めているが、図 9(b) にあるように GPU はコア数が非常に多い. この構造は大規模な行列乗算に適していて、広く使用されるようになっている. GPU が広く使われるようになるのに伴い、Tensorflowや Pytorch等、GPU を使った処理に最適化されたライブラリが盛んに開発されるようになっている.

FPGA(Field Programmable Gate Array) は、論理回路を後から変更できることが特徴のプログラマブルなハードウェアである。CPU や GPU のようなハードウェアの場合、既に論理回路設計が行われていて後から変更することはできない。しかし、FPGA はそれが可能であり、また特定の命令セットも存在しないことに伴い命令セットの解釈に必要な処理を実装する必要がないため、CPU / GPU より消費電力を削減できる可能性がある。ただし、CPU / GPU に比べて設計工数がかかるという

デメリットがある.

ASIC(Application Specific Integrated Circuit) は,直訳すると特定用途向け集積回路で,特定のアプリケーションのために最適化された回路を持つカスタムハードウェアである. ASIC は特定の用途に最適化されていて不要な回路を持たないため,他のハードウェアと比べて消費電力を抑えやすく,また同じ機能をより小さなチップサイズで実現することができる. ただし,完全にカスタマイズで開発をすることになるので,設計から製造まで多大な時間とコストがかかったり,一度製造すると回路を変更できないというデメリットもある.

## **第3章 GNN / GCN アクセラレーションの 分類**

#### 3.1 分類項目の定義

GNN / GCN のハードウェア実装は,推論レイテンシの削減,消費電力の削減,メモリアクセスの効率化等,様々な最適化目標を持っている.また,対象とする GNN の処理フェーズやデータセット,ネットワーク等,前提とする条件も論文により大きく異なる.本章では,既存研究におけるこれらの実装の傾向を明らかにするために,各手法において対象とするフェーズ,目的,データセット,ネットワーク,デバイス,および量子化精度に基づいて整理する.各分類項目の定義は次の通りである.

- ID:研究の識別番号

- ・ 論文: 方式名または著者名

- フェーズ: GNN の処理における対象フェーズ(例:推論, トレーニング)

- 目的:ハードウェア実装の主な評価観点(例:推論レイテンシの削減,消費電力の削減等)

- データセット:使用されるデータセットの種類(例:表3)

- ネットワーク:使用される GNN アーキテクチャの種類

- デバイス:使用されるデバイスの種類(ASIC, FPGA, CPU, GPU)

- 量子化精度:量子化における精度(例:32bit 固定小数点, 16bit 浮動小数点)

#### 3.2 分類表と考察

GNN / GCN のハードウェア実装の対象フェーズは,①推論(推論のみに対応),②トレーニング(トレーニングのみに対応),③推論とトレーニング(推論とトレーニングの両方に対応)の3種類に分類される.GNN / GCN ハードウェア実装の既存研究100本を,対象フェーズ毎に3.1節の分類項目に基づいて分類した結果をそれぞれ表4,表5,表6にて示す.

ハードウェア実装の全体的な傾向として,フェーズについては,推論フェーズのみを対象とする論文が75本,トレーニングフェーズのみを対象とする論文が20本,推論/トレーニングの両方のフェーズを対象とする論文が5本であり,推論フェーズを対象とする論文数が非常に多い.これは,推論は訓練済みモデルを実際の

表 3. GNN / GCN のハードウェア実装で用いられる代表的なベンチマーク用データセット. クラスは, データセット内の分類のカテゴリを表す. 例えば Cora の場合,強化学習, ニューラルネットワーク, 事例ベース, 遺伝的アルゴリズム, 確率的手法,ルール学習, 理論という 7 つの論文カテゴリが存在することを意味する. 特徴量は,各ノードに対して付与されていて, ノードの特徴を表す. 例えば Cora の場合,特徴量は論文要旨の単語の集合を表していて,使用される語彙の数は 1,433 である.

| データセット            | 説明                                          | クラス | ノード       | エッジ         | 特徴量   |

|-------------------|---------------------------------------------|-----|-----------|-------------|-------|

| Cora [3]          | 機械学習関連の<br>論文の引用関係<br>を表すデータセ<br>ット         | 7   | 2,708     | 5,429       | 1,433 |

| Citeseer [3]      | 情報科学関係の<br>論文の引用関係<br>を表すデータセット             | 6   | 3,327     | 4,732       | 3,703 |

| Pubmed [3]        | 糖尿病に関する<br>医学論文の引用<br>関係を表すデー<br>タセット       | 3   | 19,717    | 44,338      | 500   |

| PPI [4]           | タンパク質問の<br>関係を表すデー<br>タセット                  | 121 | 14,755    | 225,270     | 50    |

| Flickr [5]        | 画像共有サイトにおけるアノテーション付き画像のデータセット               | 7   | 89,250    | 899,756     | 500   |

| Yelp [5]          | ・<br>レビューサイト<br>のレビューやユ<br>ーザに関するデ<br>ータセット | 100 | 716,847   | 6,977,410   | 300   |

| Reddit [6]        | フォーラムサイ<br>トの投稿の関係<br>を表すデータセ<br>ット         | 41  | 232,965   | 11,606,919  | 602   |

| Amazon [7]        | E コマースサイ<br>トの商品の購入<br>情報を表すデー<br>タセット      | 107 | 1,598,960 | 132,169,734 | 200   |

| OGBN-Products [8] | E コマースサイトにおけるよく<br>一緒に購入される商品関係を表すデータセット    | 47  | 2,449,029 | 61,859,140  | 100   |

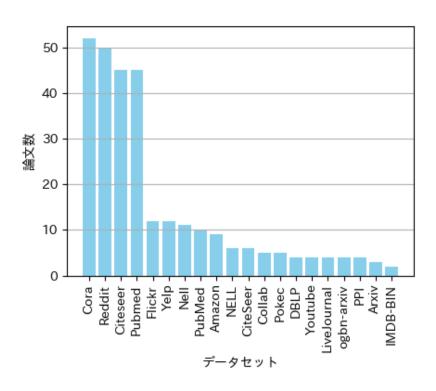

図 10: 推論のみを対象とする GNN / GCN ハードウェア実装のデータセット毎の 論文数

アプリケーションで使用する段階であり、多くの実際のアプリケーションで実行するにあたって低遅延の処理が求められていて、推論の高速化に対する需要がトレーニングと比べて高いことが要因として考えられる。また、高速化以外でも、例えばモバイルデバイスや IoT デバイスにおいては電力効率が重要な課題であり、主に推論フェーズが実行される。これらのデバイスでは、電力効率の最適化は実行時の省電力化に直接寄与するため研究分野としての需要が大きいことも要因の1つとして挙げられる。多くの論文では、推論かトレーニングかいずれかのフェーズに最適化することを目標としていて、両方に対応する論文は少ない。

目的については,大半の研究がレイテンシと消費電力の削減の2つを挙げているが,他にも,オフチップメモリアクセスの削減(HyGCN[9], AWB-GCN[10], GC-NAX[41], Zhang他 [43], I-GCN[11], ReGNN[55]等)やチップ面積の削減(ReGNN[55], COIN[13], FusedGCN[79]),オフチップメモリ帯域幅使用量の削減(GCoD[48], G-CoS[49], Accel-GCN[101])を目的とする既存研究もある. ただし,オフチップメモリアクセスの削減,チップ面積の削減,オフチップメモリ帯域幅使用量の削減等,いずれもレイテンシと消費電力の削減という最終目標を達成するための定量指標としての位置付けになっていると解釈できる.

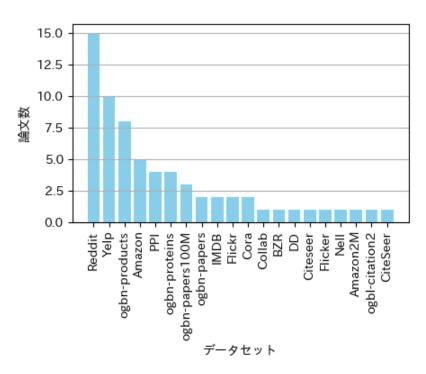

図 11: トレーニングのみを対象とする GNN / GCN ハードウェア実装のデータセット毎の論文数

データセットについて, 図 10, 図 11, 図 12 で①推論, ②トレーニング, ③推論/ トレーニングの両方の3つの対応フェーズ毎に上位20件の対象データセット を示す. ①推論の対象データセットについて, 上位 4 つの Cora, Reddit, Citeseer, Pubmed を対象としている論文は 40 本以上ありこれらが大半を占めていて, 次に Flickr, Yelp, Nell, PubMed はそれぞれ 12 本, 12 本, 11 本, 10 本あり, これら以外のデ ータセットを採用する論文数は全て10本より少ない. ①推論のみを対象とするハ ードウェア実装の上位4つのデータセットのノード/エッジ数について,表3の 通り, Cora はノード数が 2,708 でエッジ数が 5,429, Reddit はノード数が 232,965 で エッジ数が 11,606,919, Citeseer はノード数が 3,327 でエッジ数が 4,732, Pubmed はノード数が 19,717 でエッジ数が 44,338 というように, Reddit を除けば比較的ノ ード数/エッジ数が少ないデータセットが多用されている. ②トレーニングのみ を対象とするハードウェア実装については、①と同様 Reddit と、Yelp (ノード数: 716,847 / エッジ数:6,977,410), OGBN-products(ノード数:2,449,029 / エッジ 数:61,859,140), Amazon(ノード数:1,598,960 /エッジ数:132,169,734)が上 位4つで、GNN / GCN のハードウェア実装論文で取り扱うデータセットの中で も特にデータ量が多いものを採用している. これは, 推論と比べてトレーニングを 対象とする論文においては大規模なデータセットを積極的に使うことでスループ

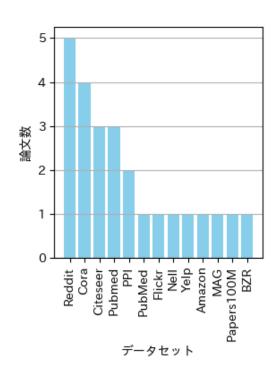

図 12: 推論/トレーニングの両方を対象とする GNN / GCN ハードウェア実装の データセット毎の論文数

ットの改善をすることを重視していることが要因だと考えられる。③推論/トレーニングの両方を対象とするハードウェア実装についても、Reddit、Cora、Citeseer、Pubmed 等、①/②と同様のデータセットが採用されている。

ネットワークについては,図13で先述の①,②,③の3つの対応フェーズ毎に上位10件の対象ネットワークを示す.これら3つ全てにおいて最も使用されているネットワークはGCNで,それぞれ68本,14本,5本と,特に①において非常に多くの論文で採用されている.また全ての対応フェーズにおいて2番目に採用されているのはGraphSAGEであり,それぞれ30本,13本,1本である.①で3番目,4番目に採用されているのは,GIN,GATで,それぞれ23本,21本で,②で3番目,4番目に採用されているのは,GAT,GINでそれぞれ6本,5本である.ネットワークについては,データセットとは異なり,推論とトレーニングのフェーズによって採用するネットワークの性質が大きく異なるということはなかった.

図 13: GNN / GCN ハードウェア実装のネットワーク毎の論文数 (a) 推論が対象 (b) トレーニングが対象 (c) 推論/トレーニングの両方が対象

図 14: GNN / GCN ハードウェア実装のデバイス毎の論文数 (a) 推論が対象 (b) トレーニングが対象 (c) 推論/トレーニングの両方が対象

デバイスについて、図 14 で対応フェーズ毎の対象デバイスにおける論文数を示す. 推論のみが対象の論文について、使用されているデバイスの大半が ASIC と FPGA であり、全体の 89.3% を占めている. 他にも、計算特性に応じて CPU / GPU を使い分けている論文 (Zhang 他 [73], MergePathSpMM[112], SEIGN[101], TGOpt[103])、GPU / ASIC を使い分けている論文 (Jin[88], Slice-and-Forge[89]) がある. トレーニングのみが対象の論文については、ASIC が7件と最も多く、次にGPU が5件、CPU / FPGA が4件と続く. 推論のみを対象とする論文では GPU のみを採用している論文は1件しかないが、トレーニングのみを対象とする論文は5件あった. 推論/トレーニングの両方が対象の論文では、5件中4件が ASIC である.

量子化精度については, 論文中で明示されていないものも半数近くあるが, 明示されているものの中では, 特徴ベクトル/重みベクトルにおいて 32bit 固定小数点/32bit 浮動小数点が多く採用されていて, 中には 16bit, 8bit を採用している論文もある. さらに精度が低い論文として, 4bit 固定小数点を採用している手法(COIN[13]), 1bit を採用している手法(Bi-GCN[128])もある.

## 表 4. 推論のみを対象とする GNN / GCN ハードウェア実装の既存研究の分類

| ID | 論文              | 目的                                                                                                                                                                                | データセット                                                                                                      | ネットワーク                                                | デバイス   | 量子化精度                                                                             |

|----|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|--------|-----------------------------------------------------------------------------------|

| 1  | HyGCN[9]        | <ul><li>・レイテンシ削減</li><li>・消費電力削減</li><li>・オフチップメモリアクセス数の削減</li><li>・DRAM 帯域幅利用率の向上</li></ul>                                                                                      | • IMDB-BIN • Cora • Citeseer • COLLAB • Pubmed • Reddit                                                     | • GCN • Graph- SAGE • GINConv • DiffPool              | • ASIC | <ul><li>特徴ベクトル:</li><li>32bit 固定小数点</li><li>重みベクトル:</li><li>32bit 固定小数点</li></ul> |

| 2  | AWB-<br>GCN[10] | <ul> <li>・レイテンシ削減</li> <li>・消費電力削減</li> <li>・オフチップメモリアクセス数の削減</li> <li>・メモリ帯域幅利用率の向上</li> <li>・Adaptive Logic Modul使用量の削減</li> <li>・オンチップストレージ需要の削減</li> <li>・PE使用率の向上</li> </ul> | <ul><li>Cora</li><li>Citeseer</li><li>Pubmed</li><li>Nell</li><li>Reddit</li></ul>                          | • GCN                                                 | • FPGA | N/A                                                                               |

| 3  | EnGN[39]        | <ul><li>・レイテンシ削減</li><li>・消費電力削減</li><li>・チップ面積削減</li><li>・I/O コスト削減</li></ul>                                                                                                    | • Cora • PubMed • Nell • CoraFull • Reddit • Enwiki • Amazon • Synthetic- A/B/C/D • AIFB • MUTAG • BGS • AM | • GCN<br>• GS-Pool<br>• Gated-GCN<br>• GRN<br>• R-GCN | • ASIC | <ul><li>特徴ベクトル: 32bit 固定小数点</li><li>重みベクトル: 32bit 固定小数点</li></ul>                 |

| 4  | Auten 他<br>[40] | <ul><li>・レイテンシ削減</li><li>・メモリ帯域幅利用率</li><li>の向上</li></ul>                                                                                                                         | <ul><li>Cora</li><li>Citeseer</li><li>Pubmed</li><li>QM9</li><li>DBLP</li></ul>                             | • GCN<br>• GAT<br>• MPNN<br>• PGNN                    | • ASIC | <ul><li>特徴ベクトル:</li><li>32bit 固定小数点</li><li>重みベクトル:</li><li>32bit 固定小数点</li></ul> |

| 5  | GC-<br>NAX[41]  | <ul><li>・レイテンシ削減</li><li>・オフチップメモリアクセス数の削減</li><li>・消費電力削減</li><li>・チップ面積削減</li></ul>                                                                                             | • Cora • Citeseer • Pubmed • Nell • Reddit                                                                  | • GCN                                                 | • ASIC | <ul><li>特徴ベクトル:<br/>64bit 倍精度浮動小数点数</li><li>重みベクトル:<br/>64bit 倍精度浮動小数点数</li></ul> |

| 6  | GRIP[42]        | <ul><li>・レイテンシ削減</li><li>・オンチップメモリ容量の削減</li></ul>                                                                                                                                 | <ul><li>Youtube</li><li>Livejournal</li><li>Pokec</li><li>Reddit</li></ul>                                  | • GCN • Graph- SAGE • G-GCN • GIN                     | • ASIC | <ul><li>特 徴 ベクトル: 16bit 固定小数点</li><li>重 み ベクトル: 16bit 固定小数点</li></ul>             |

| 7  | Zhang 他<br>[43] | <ul><li>・レイテンシ削減</li><li>・オフチップメモリアクセス数の削減</li></ul>                                                                                                                              | <ul><li>Flickr</li><li>Reddit</li><li>Yelp</li></ul>                                                        | • GCN                                                 | • FPGA | N/A                                                                               |

| 8  | I-<br>GCN[11]   | <ul><li>・レイテンシ削減</li><li>・オフチップメモリアクセス数の削減</li><li>・消費電力の削減</li></ul>                                                                                                             | • Cora • Citeseer • Pubmed • Nell • Reddit                                                                  | • GCN<br>• Graph-<br>SAGE<br>• GIN                    | • FPGA | N/A                                                                               |

| ID | 論文                          | 目的                                                                                     | データセット                                                                                                                  | ネットワーク                                   | デバイス   | 量子化精度                                                                             |

|----|-----------------------------|----------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|------------------------------------------|--------|-----------------------------------------------------------------------------------|

| 9  | Poly-<br>graph[44]          | <ul><li>・レイテンシ削減</li><li>・オフチップメモリアクセス数の削減</li><li>・消費電力の削減</li><li>・チップ面積削減</li></ul> | • Orku • LiveJournal • Twitter • IndoChina • RdUSE • RdUSW • CF • Big-mlens • Mlens • Pubmed • Cora                     | • GCN                                    | • FPGA | N/A                                                                               |

| 10 | Boost-<br>GCN[45]           | <ul><li>・レイテンシ削減</li><li>・オフチップメモリアクセス数の削減</li><li>・DRAM レイテンシの削減</li></ul>            | • Flickr<br>• Reddit<br>• Yelp<br>• Amazon                                                                              | • GCN                                    | • FPGA | <ul><li>特徴ベクトル:</li><li>32bit 浮動小数点</li><li>重みベクトル:</li><li>32bit 浮動小数点</li></ul> |

| 11 | Block-<br>GNN[46]           | ・レイテンシ削減<br>・消費電力削減                                                                    | <ul><li>Cora</li><li>Citeseer</li><li>Pubmed</li><li>Reddit</li></ul>                                                   | • GCN<br>• G-GCN<br>• GS-Pool<br>• GAT   | • FPGA | <ul><li>特徴ベクトル:</li><li>32bit 固定小数点</li><li>重みベクトル:</li><li>32bit 固定小数点</li></ul> |

| 12 | Deep-<br>Burning-<br>GL[47] | <ul><li>・レイテンシ削減</li><li>・消費電力削減</li></ul>                                             | <ul><li>Cora</li><li>Pubmed</li><li>Reddit</li><li>AIFB</li><li>MUTAG</li><li>BGS</li><li>AM</li><li>ModelNet</li></ul> | • GCN • GC-Pool • R-GCN • EdgeConv       | • FPGA | <ul><li>特徴ベクトル: 16bit 固定小数点</li><li>重みベクトル: 16bit 固定小数点</li></ul>                 |

| 13 | GCoD[48]                    | <ul><li>・レイテンシ削減</li><li>・オフチップメモリ帯域幅使用量の削減</li><li>・オフチップメモリアクセス数の削減</li></ul>        | Cora     Citeseer     Pubmed     NELL     OGBN- arxiv     Reddit                                                        | • GCN • GIN • Graph- SAGE • GAT • ResGCN | • FPGA | <ul><li>特徴ベクトル:</li><li>8bit 固定小数点</li><li>重みベクトル:</li><li>8bit 固定小数点</li></ul>   |

| 14 | G-<br>CoS[49]               | <ul><li>・レイテンシ削減</li><li>・オフチップメモリ帯域幅使用量の削減</li></ul>                                  | • Cora<br>• Citeseer<br>• Pubmed<br>• Reddit                                                                            | • GCN • GAT • GIN • Graph- SAGE          | • FPGA | <ul><li>特徴ベクトル:<br/>16bit 固定小数点</li><li>重みベクトル:<br/>16bit 固定小数点</li></ul>         |

| 15 | Chen 他<br>[50]              | <ul><li>レイテンシ削減</li><li>processing unit の利用率の向上</li></ul>                              | <ul><li>Blogcatalog</li><li>Citeseer</li><li>Coauthor</li><li>DBLP</li><li>Pubmed</li></ul>                             | • DAGNN • GCN • GWNN • SGC               | • CPU  | N/A                                                                               |

| 16 | Huang 他<br>[51]             | <ul><li>・レイテンシ削減</li><li>・スループットの向上<br/>消費電力の削減</li></ul>                              | • Cora<br>• Citeseer<br>• Pubmed<br>• Nell<br>• Reddit                                                                  | • GCN • GIN • GAT • Graph- SAGE          | • ASIC | <ul><li>特 徴 ベクトル:<br/>32bit 固定小数点</li><li>重 み ベクトル:<br/>32bit 固定小数点</li></ul>     |

| ID | 論文            | 目的                          | データセット                                  | ネットワーク               | デバイス   | 量子化精度          |

|----|---------------|-----------------------------|-----------------------------------------|----------------------|--------|----------------|

| 17 | Tailor 他      | <ul><li>レイテンシ削減</li></ul>   | • Reddit                                | • GCN                | • ASIC | ・特徴ベクトル:       |

|    | [52]          | <ul><li>オフチップメモリ使</li></ul> | • Code                                  | • GIN                |        | 32bit 浮動小数点    |

|    |               | 用量の削減                       | • Arxiv                                 | • Graph-             |        | ・重みベクトル:       |

|    |               |                             | • ZINV                                  | SAGE                 |        | 32bit 浮動小数点    |

|    |               |                             |                                         | • GAT                |        |                |

|    |               |                             |                                         | • MPNN               |        |                |

|    |               |                             |                                         | • PNA                |        |                |

|    |               | Wri N-A                     |                                         | • EGC                |        |                |

| 18 | Cambricon     |                             | • YouTube                               | • GCN                | • ASIC | N/A            |

|    | -G[53]        | <ul><li>キャッシュミス率の</li></ul> | • Flickr                                | • Graph-             |        |                |

|    |               | 改善<br>  消費電力の削減             | • Pokec                                 | SAGE • DiffPool      |        |                |

|    |               |                             | • Reddit                                |                      |        |                |

|    |               |                             | • D&D<br>• MN40                         | • EdgeConv<br>• DGMG |        |                |

|    |               |                             |                                         | • GUN                |        |                |

|    |               |                             | <ul><li>Cycle</li><li>Colors</li></ul>  | GUN                  |        |                |

|    |               |                             | • Enzymes                               |                      |        |                |

| 19 | Challanalle   | <ul><li>レイテンシ削減</li></ul>   | • Reddit                                | • GCN                | • ASIC | N/A            |

| 1) | 他 [54]        | 消費電力の削減                     | • Pubmed                                | GCIV                 | ASIC   |                |

|    | 12 [3 i]      | 们负电/3·2/11///               | • Citeseer                              |                      |        |                |

|    |               |                             | • Cora                                  |                      |        |                |

|    |               |                             | • Collab                                |                      |        |                |

| 20 | Re-           | <ul><li>レイテンシ削減</li></ul>   | • Cora                                  | • GCN                | • ASIC | N/A            |

|    | GNN[55]       | • オフチップメモリア                 | • BZR                                   | • GS-Pool            |        |                |

|    |               | クセス数の削減                     | • PPI                                   | • G-GCN              |        |                |

|    |               | • 消費電力の削減                   | • Reddit                                |                      |        |                |

|    |               | • チップ面積の削減                  | • IMDB                                  |                      |        |                |

|    |               |                             | • Collab                                |                      |        |                |

| 21 | GN-           | • レイテンシ削減                   | • Cora                                  | • GCN                | • ASIC | N/A            |

|    | Nerator       |                             | • Citeseer                              | • Graph-             |        |                |

|    | [56]          |                             | • Pubmed                                | SAGE                 |        |                |

|    |               |                             |                                         | • Graph-             |        |                |

| 22 | DIL           | 4dhV                        |                                         | SagePool             | L GIG  | 27/4           |

| 22 | PIM-          | ・レイテンシ削減                    | • Cora                                  | • GCN                | • ASIC | N/A            |

|    | GCN[57]       | • 消費電力の削減                   | • Citeseer                              | • Graph-             |        |                |

|    |               |                             | <ul><li>Pubmed</li><li>Reddit</li></ul> | SAGE                 |        |                |

| 23 | H-            | <br>・レイテンシ削減                | • Reddit                                | • GIN                | • ASIC | N/A            |

| 23 | н-<br>GCN[58] | - ドレイテンシ 削減<br>- 消費電力の削減    | • Cora<br>• Citeseer                    | JUIN                 | ASIC   | 1N/A           |

|    | GCN[36]       | * 伯其电力》的颁                   | • Pubmed                                |                      |        |                |

|    |               |                             | • Flickr                                |                      |        |                |

|    |               |                             | • Reddit                                |                      |        |                |

|    |               |                             | • Yelp                                  |                      |        |                |

|    |               |                             | • Amazon                                |                      |        |                |

| 24 | LW-           | <ul><li>レイテンシ削減</li></ul>   | • Cora                                  | • GCN                | • FPGA | ・特徴ベクトル:       |

|    | GCN[59]       | • 消費電力の削減                   | • Citeseer                              | • Graph-             |        | 16bit 固定小数点    |

|    |               |                             | • Pubmed                                | SAGE                 |        | ・重みベクトル:       |

|    |               |                             |                                         |                      |        | 16bit 固定小数点    |

|    |               |                             |                                         |                      |        | • 隣接行列の非ゼロ     |

|    |               |                             |                                         |                      |        | 要素: 4bit 固定小数  |

|    |               |                             |                                         |                      |        | 点              |

|    |               |                             |                                         |                      |        | • 中間表現:32bit 固 |

|    |               |                             |                                         |                      |        | 定小数点           |

| ID | 論文                | 目的                                                             | データセット                                                                                                                                  | ネットワーク                                         | デバイス   | 量子化精度                                                                             |

|----|-------------------|----------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------|--------|-----------------------------------------------------------------------------------|

| 25 | Versa-<br>GNN[60] | <ul><li>・レイテンシ削減</li><li>・スループットの向上</li><li>・消費電力の削減</li></ul> | <ul><li>Cora</li><li>Citeseer</li><li>Pubmed</li><li>IMDB-BIN</li><li>Reddit</li><li>Amazon</li><li>Collab</li></ul>                    | • GCN • Graph- SAGE • GIN • GAT                | • ASIC | <ul><li>特徴ベクトル:</li><li>16bit 浮動小数点</li><li>重みベクトル:</li><li>32bit 浮動小数点</li></ul> |

| 26 | DyGNN<br>[61]     | ・レイテンシ削減<br>・推論精度の向上                                           | <ul><li>Cora</li><li>Citeseer</li><li>Pubmed</li><li>Reddit</li></ul>                                                                   | • GCN<br>• GAT                                 | • ASIC | N/A                                                                               |

| 27 | FPGAN<br>[62]     | ・レイテンシ削減<br>・消費電力の削減                                           | Cora     Citeseer     Pubmed                                                                                                            | • GAT                                          | • FPGA | <ul><li>特徴ベクトル:<br/>8bit 固定小数点</li><li>重みベクトル:<br/>4bit 固定小数点</li></ul>           |

| 28 | Lin-<br>他 [63]    | ・レイテンシ削減<br>・消費電力の削減                                           | <ul><li>Amazon</li><li>Reddit</li><li>Yelp</li></ul>                                                                                    | • GCN                                          | • FPGA | N/A                                                                               |

| 29 | Kwon-<br>他 [64]   | ・レイテンシ削減<br>・消費電力の削減                                           | Chmleon Citeseer Coraml Dblpfull CS Corafull Physics Road-tx Road-pa Youtube Road-ca Wikitalk Ijournal                                  | • GCN<br>• Graph-<br>SAGE                      | • FPGA | N/A                                                                               |

| 30 | COIN[13]          | <ul><li>・レイテンシ削減</li><li>・消費電力の削減</li><li>・チップ面積の削減</li></ul>  | <ul><li>Cora</li><li>Citeseer</li><li>Pubmed</li><li>Nell</li><li>Extended</li><li>Cora</li></ul>                                       | • GCN                                          | • ASIC | <ul><li>特徴ベクトル:<br/>4bit 固定小数点</li><li>重みベクトル:<br/>4bit 固定小数点</li></ul>           |

| 31 | GROW<br>[65]      | <ul><li>・消費電力の削減</li><li>・メモリ使用量の削減</li></ul>                  | <ul> <li>Cora</li> <li>Citeseer</li> <li>Pubmed</li> <li>Flickr</li> <li>Reddit</li> <li>Yelp</li> <li>Pokec</li> <li>Amazon</li> </ul> | • GCN                                          | • ASIC | N/A                                                                               |

| 32 | Ding<br>他 [66]    | ・消費電力の削減 ・スループットの向上                                            | • Kinetics • NTU- RGB+D                                                                                                                 | • GCN                                          | • FPGA | <ul><li>特徴ベクトル:<br/>16bit 固定小数点</li><li>重みベクトル:<br/>16bit 固定小数点</li></ul>         |

| 33 | GNNIE<br>[67]     | <ul><li>レイテンシ削減</li></ul>                                      | • Cora • Citeseer • Pubmed • Reddit • PPI                                                                                               | • GCN • GAT • Graph- SAGE • GINConv • DiffPool | • ASIC | N/A                                                                               |

| ID | 論文                     | 目的                                                                   | データセット                                                                                    | ネットワーク                                   | デバイス           | 量子化精度                                                                             |

|----|------------------------|----------------------------------------------------------------------|-------------------------------------------------------------------------------------------|------------------------------------------|----------------|-----------------------------------------------------------------------------------|

| 34 | ACE-GCN[68]            | <ul><li>レイテンシ削減</li></ul>                                            | • Cora • Citeseer • PubMed • NELL • Reddit • Cont-201 • Fome20 • D6-6                     | • GCN                                    | • FPGA         | N/A                                                                               |

| 35 | CoDG-<br>ReRAM<br>[69] | ・レイテンシ削減<br>・消費電力の削減                                                 | • Cora • Citeseer • Pubmed                                                                | • GCN                                    | • ASIC         | ・特徴ベクトル: N/<br>A<br>・重みベクトル:<br>2bit/4bit/8bit                                    |

| 36 | Flow-<br>GNN[70]       | ・レイテンシ削減<br>・消費電力の削減                                                 | • Cora • CiteSeer • PubMed • Reddit • MolHIV • MolPCBA • HEP                              | • GCN • GIN • GIN + VN • GAT • PNA • DGN | • FPGA         | N/A                                                                               |

| 37 | FP-<br>GNN[71]         | ・レイテンシ削減<br>・消費電力の削減                                                 | • Cora • Citeseer • Pubmed • Reddit                                                       | • GCN • Graph- SAGE • GAT                | • FPGA         | <ul><li>特徴ベクトル:</li><li>32bit 固定小数点</li><li>重みベクトル:</li><li>32bit 固定小数点</li></ul> |

| 38 | Sun<br>他 [72]          | <ul><li>・レイテンシ削減</li><li>・消費電力の削減</li><li>・オフチップメモリアクセスの削減</li></ul> | Reddit     OGB     LiveJournal                                                            | • GCN • GIN • Graph- SAGE                | • FPGA         | <ul><li>特徴ベクトル:</li><li>32bit 固定小数点</li><li>重みベクトル:</li><li>32bit 固定小数点</li></ul> |

| 39 | Zhang<br>他 [73]        | <ul><li>レイテンシ削減</li></ul>                                            | • Flickr • Reddit • OGBN- arxiv                                                           | • GCN • Graph- SAGE • GIN • GAT          | • CPU<br>• GPU | <ul><li>特徴ベクトル:</li><li>32bit 浮動小数点</li><li>重みベクトル:</li><li>32bit 浮動小数点</li></ul> |

| 40 | ReGNN<br>[74]          | <ul><li>レイテンシ削減</li></ul>                                            | <ul><li>Cora</li><li>Citeseer</li><li>Pubmed</li><li>Reddit</li></ul>                     | • GCN<br>• GS-Pool                       | • ASIC         | N/A                                                                               |

| 41 | Li 他<br>[75]           | <ul><li>レイテンシ削減</li></ul>                                            | Citeseer     Collab     Pubmed                                                            | • GCN • GIN • Graph- SAGE                | • ASIC         | N/A                                                                               |

| 42 | ReaDy<br>[76]          | • レイテンシ削減                                                            | <ul><li> HepTH</li><li> Imdb</li><li> Epinions</li><li> Flickr</li><li> Youtube</li></ul> | • CD-GCN<br>• TGCN<br>• MPNN-<br>LSTM    | • ASIC         | <ul><li>特徴ベクトル:</li><li>32bit 固定小数点</li><li>重みベクトル:</li><li>32bit 固定小数点</li></ul> |

| 43 | PAS-<br>GCN[77]        | <ul><li>レイテンシ削減</li></ul>                                            | • Cora • Citeseer • Pubmed • Reddit                                                       | • GCN                                    | • ASIC         | N/A                                                                               |

| ID | 論文                | 目的                                                            | データセット                                                                                                                         | ネットワーク                                                | デバイス            | 量子化精度                                                                             |

|----|-------------------|---------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|-----------------|-----------------------------------------------------------------------------------|

| 44 | Flow-<br>GNN[78]  | ・レイテンシ削減<br>・消費電力の削減                                          | • MolHIV • MolPCBA • HEP (High Energy Physics) • Cora • CiteSeer • PubMed • Reddit                                             | • GIN<br>• GIN+VN<br>• GCN<br>• GAT<br>• PNA<br>• DGN | • FPGA          | N/A                                                                               |

| 45 | Fused-<br>GCN[79] | <ul><li>・レイテンシ削減</li><li>・消費電力の削減</li><li>・チップ面積の削減</li></ul> | <ul><li>Cora</li><li>Citeseer</li><li>Pubmed</li><li>Reddit</li><li>Nell</li></ul>                                             | • GCN                                                 | • ASIC          | N/A                                                                               |

| 46 | Jin<br>他 [80]     | <ul><li>レイテンシ削減</li></ul>                                     | <ul><li>Cora</li><li>Citeseer</li><li>Pubmed</li><li>Nell</li><li>Reddit</li></ul>                                             | • GCN                                                 | • GPU<br>• ASIC | N/A                                                                               |

| 47 | ZIPPER[81         | ]・レイテンシ削減<br>・消費電力の削減                                         | • ak2010 • coAuthorsD-BLP • hollywood-2009 • cit-Patents • soc-LiveJournal1 • europe-osm • Cora • Citeseer • Pubmed • Reddit   | • GAT • Graph- SAGE • VGG • ResNET • PageRank         | • ASIC          | N/A                                                                               |

| 48 | EGCN[82]          | <ul><li>・オフチップメモリア<br/>クセス数の削減</li><li>・消費電力の削減</li></ul>     | <ul><li>Cora</li><li>CiteSeer</li><li>PubMed</li><li>Nell</li><li>Flickr</li><li>Reddit</li><li>Reddit2</li><li>Yelp</li></ul> | • GCN                                                 | • ASIC          | <ul><li>特徴ベクトル:</li><li>32bit 固定小数点</li><li>重みベクトル:</li><li>32bit 固定小数点</li></ul> |

| 49 | Yoo<br>他 [83]     | <ul><li>レイテンシ削減</li></ul>                                     | <ul><li>Wiki</li><li>Pokec</li><li>Youtube</li><li>LiveJournal</li></ul>                                                       | • GCN                                                 | • ASIC          | <ul><li>特徴ベクトル:</li><li>32bit 固定小数点</li><li>重みベクトル:</li><li>32bit 固定小数点</li></ul> |

| 50 | GPG-<br>CN[84]    | ・レイテンシ削減                                                      | <ul><li>Cora</li><li>Citeseer</li><li>Pubmed</li><li>Nell</li></ul>                                                            | • GCN<br>• GAT                                        | • ASIC          | <ul><li>特徴ベクトル: 32bit 単精度浮動小数点</li><li>重みベクトル: 32bit 単精度浮動小数点</li></ul>           |

| ID | 論文                          | 目的                                               | データセット                                                                                                                                               | ネットワーク                                | デバイス            | 量子化精度                                                                                                                     |

|----|-----------------------------|--------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|-----------------|---------------------------------------------------------------------------------------------------------------------------|

| 51 | SGCN[85]                    | <ul><li>レイテンシ削減</li></ul>                        | <ul> <li>Cora</li> <li>CiteSeer</li> <li>PubMed</li> <li>NELL</li> <li>Reddit</li> <li>Flickr</li> <li>Yelp</li> <li>DBLP</li> <li>GitHub</li> </ul> | • GCN • GINConv • Graph- SAGE         | • ASIC          | N/A                                                                                                                       |

| 52 | Zhu<br>他 [86]               | <ul><li>・レイテンシ削減</li><li>・消費電力の削減</li></ul>      | <ul><li>Cora</li><li>Citeseer</li><li>Pubmed</li><li>Arxiv</li><li>Reddit</li></ul>                                                                  | • GCN                                 | • ASIC          | <ul><li>・特徴ベクトル: 12 or 8 bit 固定小数点</li><li>・重みベクトル: 12 or 8 bit 固定小数点</li></ul>                                           |

| 53 | QE-<br>GCN[87]              | <ul><li>・レイテンシ削減</li><li>・消費電力の削減</li></ul>      | • Cora<br>• Citeseer<br>• Pubmed                                                                                                                     | • GCN                                 | • FPGA          | <ul> <li>特徴ベクトル: 8</li> <li>or 16 or 32 bit 固定<br/>小数点</li> <li>・重みベクトル: 8</li> <li>or 16 or 32 bit 固定<br/>小数点</li> </ul> |

| 54 | Graph-<br>AGILE<br>[88]     | <ul><li>レイテンシ削減</li></ul>                        | <ul> <li>Cora</li> <li>Citeseer</li> <li>Pubmed</li> <li>PPI</li> <li>Reddit</li> <li>Yelp</li> <li>Amazon-<br/>Products</li> </ul>                  | • GCN • GAT • GIN • Graph- SAGE • SGC | • FPGA          | N/A                                                                                                                       |

| 55 | Slice-<br>and-<br>Forge[89] | <ul><li>レイテンシ削減</li></ul>                        | <ul><li>Products</li><li>Citation</li><li>Pokec</li><li>YouTube</li><li>LiveJournal</li><li>Orkut</li><li>Reddit</li></ul>                           | • GCN                                 | • GPU<br>• ASIC | <ul><li>特徴ベクトル:</li><li>32bit 固定小数点</li><li>重みベクトル:</li><li>32bit 固定小数点</li></ul>                                         |

| 56 | Stream-<br>GCN[90]          | <ul><li>レイテンシ削減</li></ul>                        | • AIDS                                                                                                                                               | • GCN                                 | • FPGA          | N/A                                                                                                                       |

| 57 | Cheng<br>他 [91]             | • レイテンシ削減                                        | Cora     Citeseer     Pubmed                                                                                                                         | • GCN                                 | • FPGA          | <ul><li>特 徴 ベクトル:</li><li>32bit 浮動小数点</li><li>重 み ベクトル:</li><li>32bit 浮動小数点</li></ul>                                     |

| 58 | NT-<br>GAT[92]              | <ul><li>・レイテンシ削減</li><li>・消費電力の削減</li></ul>      | • Cora • Citeseer • Pubmed • OGBN- arxiv • Reddit                                                                                                    | • GCN                                 | • FPGA          | N/A                                                                                                                       |

| 59 | GCIM<br>[93]                | <ul><li>・レイテンシ削減</li><li>・メモリアクセス時間の削減</li></ul> | <ul><li>Cora</li><li>Citeseer</li><li>Pubmed</li><li>DBLP</li><li>Reddit</li></ul>                                                                   | • GCN<br>• Graph-<br>SAGE<br>• GIN    | • ASIC          | N/A                                                                                                                       |

| ID | 論文                             | 目的                                                                 | データセット                                                                                                                                                                               | ネットワーク                             | デバイス           | 量子化精度                                                                                         |

|----|--------------------------------|--------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|----------------|-----------------------------------------------------------------------------------------------|

| 60 | MEGA<br>[94]                   | <ul><li>・レイテンシ削減</li><li>・消費電力の削減</li></ul>                        | • Cora • CiteSeer • PubMed • NELL • Reddit                                                                                                                                           | • GCN • GIN • Graph- SAGE          | • ASIC         | N/A                                                                                           |

| 61 | Shen<br>他 [95]                 | <ul><li>・レイテンシ削減</li><li>・消費電力の削減</li></ul>                        | <ul><li>MovieLens-<br/>100K</li><li>Gowalla</li><li>Yelp</li><li>MovieLens-<br/>10M</li></ul>                                                                                        | • GCMC<br>• NGCF<br>• LightGCN     | • ASIC         | N/A                                                                                           |

| 62 | Merge<br>Path-<br>SpMM<br>[96] | ・レイテンシ削減・消費電力の削減                                                   | • Cora • Citeseer • Pubmed • Oregon-1 • As-caida • Wiki-Vote • Nell • PPI • Amazon • coAuthorsD-BLP • soc-BlogCatalog • PROTEINS • Twitter-partial • DD • Yeast • OVCAR-8H • SW-620H | • GCN                              | • CPU<br>• GPU | N/A                                                                                           |

| 63 | Ran<br>他 [97]                  | •レイテンシ削減                                                           | <ul><li>PubMed</li><li>Flickr</li><li>Reddit</li><li>Yelp</li></ul>                                                                                                                  | • GCN                              | • FPGA         | <ul><li>特徴ベクトル: 8</li><li>or 12 bit 固定小数点</li><li>重みベクトル: 8</li><li>or 12 bit 固定小数点</li></ul> |

| 64 | CoGNN<br>[98]                  | <ul><li>・レイテンシ削減</li><li>・演算ユニットの利用率の改善</li><li>・消費電力の削減</li></ul> | • Reddit • OGBN- Products • OGBN- Papers • Yelp                                                                                                                                      | • GCN<br>• Graph-<br>SAGE<br>• GIN | • ASIC         | ・特徴ベクトル: 8<br>or 12 bit 固定小数点<br>・重みベクトル: 8<br>or 12 bit 固定小数点                                |

| 65 | FTW-<br>GAT<br>[99]            | ・レイテンシ削減<br>・消費電力の削減                                               | Cora     Citeseer     Pubmed                                                                                                                                                         | • GAT                              | • FPGA         | <ul><li>特徴ベクトル:</li><li>8bit 固定小数点</li><li>重みベクトル:</li><li>2bit 固定小数点</li></ul>               |

| 66 | Nair<br>他 [100]                | • レイテンシ削減                                                          | <ul><li>Cora</li><li>Citeseer</li><li>Pubmed</li><li>Reddit</li></ul>                                                                                                                | • GCN                              | • FPGA         | <ul><li>特徴ベクトル:<br/>8bit 固定小数点</li><li>重みベクトル:<br/>8bit 固定小数点</li></ul>                       |

| 67 | Accel-<br>GCN[101]             | ・オフチップメモリ帯<br>域幅使用量の削減                                             | • am • Arxiv • com- amazon • Pubmed • SW-620H • Yelp                                                                                                                                 | • GCN • GIN • Graph- SAGE          | • GPU          | N/A                                                                                           |

| ID | 論文             | 目的                                        | データセット                                      | ネットワーク           | デバイス   | 量子化精度                           |

|----|----------------|-------------------------------------------|---------------------------------------------|------------------|--------|---------------------------------|

| 68 | SEIGN          | • 推論精度の向上                                 | • UCI                                       | • GCN            | • CPU  | N/A                             |

|    | [102]          |                                           | Bitcoin                                     | • GAT            | • GPU  |                                 |

|    |                |                                           | • ogbl-collab                               | • SEIGN          |        |                                 |

|    |                |                                           | Company                                     |                  |        |                                 |

| 69 | IMGA           | <ul><li>レイテンシ削減</li></ul>                 | • Cora                                      | • GCN            | • ASIC | ・特徴ベクトル:                        |

|    | [103]          |                                           | • Pubmed                                    |                  |        | 8bit 固定小数点                      |

|    |                |                                           | • Citeseer                                  |                  |        | ・重みベクトル:                        |

|    |                |                                           | • OGBN-                                     |                  |        | 8bit 固定小数点                      |

|    |                |                                           | arxiv                                       |                  |        |                                 |

|    |                |                                           | • Ogbl-collab                               |                  |        |                                 |

|    |                |                                           | <ul><li>Ogbl-ppa</li><li>Reddit</li></ul>   |                  |        |                                 |

| 70 | TGOpt          | <br>・レイテンシ削減                              | • jodie-lastfm                              | • TGAT           | • CPU  | ・特徴ベクトル:                        |

| /0 | 100pt<br>[104] | ・レイノン自動機                                  | • jodie-mooc                                | · IUAI           | • GPU  | 32bit 浮動小数点                     |

|    | [104]          |                                           | • jodie-reddit                              |                  | GFU    | <ul><li>・重みベクトル:</li></ul>      |

|    |                |                                           | • jodie-wiki                                |                  |        | 32bit 浮動小数点                     |

|    |                |                                           | • snap-email                                |                  |        | 3201( 1) ±0/1 (32.//)           |

|    |                |                                           | • snap-msg                                  |                  |        |                                 |

|    |                |                                           | • snap-reddit                               |                  |        |                                 |

| 71 | GHOST          | • 推論の改善                                   | • Cora                                      | • GCN            | • ASIC | ・特徴ベクトル:                        |

|    | [105]          | • 消費電力の削減                                 | • PubMed                                    | • GAT            |        | 8bit 固定小数点                      |

|    |                |                                           | • Citeseer                                  | • Graph-         |        | • 重みベクトル:                       |

|    |                |                                           | Amazon                                      | SAGE             |        | 8bit 固定小数点                      |

|    |                |                                           | • Proteins                                  | • GIN            |        |                                 |

|    |                |                                           | Mutag                                       |                  |        |                                 |

|    |                |                                           | • BZR                                       |                  |        |                                 |

|    |                |                                           | • IMDB-                                     |                  |        |                                 |

|    |                | With S. D.                                | binary                                      |                  |        | file Add a second               |

| 72 | NEM-           | ・レイテンシ削減                                  | • Cora                                      | • GCN            | • ASIC | ・特徴ベクトル:                        |

|    | GNN            | • スループットの向上 ※ 典索力の判決                      | • Citeseer                                  | • GAT            |        | 8bit 固定小数点<br>• 重 み ベ ク ト ル:    |

|    | [106]          | ・消費電力の削減                                  | • Pubmed • Reddit                           | • Graph-<br>SAGE |        | • 単 み ヘ ク 下 ル:  <br>8bit 固定小数点  |

|    |                |                                           | • Twitter                                   | SAGE             |        | oult 回足小数点                      |

| 73 | Chen           | <br>・レイテンシ削減                              | • Cora                                      | • GCN            | • FPGA | N/A                             |

| 13 | 他 [107]        | - V ( ) V ( ) ( ) ( ) ( ) ( ) ( ) ( ) ( ) | • Citeseer                                  | • Graph-         | IIIGA  | IV/A                            |

|    | 12 [107]       |                                           | • Pubmed                                    | SAGE             |        |                                 |

|    |                |                                           | • Flickr                                    | • GIN            |        |                                 |

|    |                |                                           | • NELL                                      | • SGC            |        |                                 |

|    |                |                                           | • Reddit                                    |                  |        |                                 |

| 74 | Dyna-          | <ul><li>レイテンシ削減</li></ul>                 | • Cora                                      | • GCN            | • FPGA | N/A                             |

|    | sparse         |                                           | • CiteSeer                                  | • Graph-         |        |                                 |

|    | [108]          |                                           | • PubMed                                    | SAGE             |        |                                 |

|    |                |                                           | • Flickr                                    | • GIN            |        |                                 |

|    |                |                                           | • NELL                                      | • SGC            |        |                                 |

|    | CORT           | 4-/ 11/1/                                 | • Reddit                                    | COL              | ED.C.  | <b>肚</b>                        |

| 75 | GNN-           | <ul><li>レイテンシ削減</li></ul>                 | • QM9                                       | • GCN            | • FPGA | •特徴ベクトル:                        |

|    | Builder        |                                           | • ESOL                                      | • Graph-         |        | 16bit 固定小数点                     |

|    | [109]          |                                           | • FreeSolv                                  | SAGE<br>• GIN    |        | • 重 み ベ ク ト ル:  <br>32bit 固定小数点 |

|    |                |                                           | <ul><li>Lipophilicity</li><li>HIV</li></ul> | • GIN<br>• PNA   |        | 32011 回足小数品                     |

|    |                |                                           | - 111 A                                     | - I INA          |        |                                 |

表 5. トレーニングのみを対象とする GNN / GCN ハードウェア実装の既存研究 の分類

| ID | 論文             | 目的                                          | データセット                                   | ネットワーク           | デバイス            | 量子化精度        |

|----|----------------|---------------------------------------------|------------------------------------------|------------------|-----------------|--------------|

| 76 | Graph-         | <ul><li>レイテンシ削減</li></ul>                   | • PPI                                    | • Graph-         | • CPU           | ・特徴ベクトル:     |

|    | ACT[110]       | • DSP 利用率向上                                 | • Reddit                                 | SAGE             | • FPGA          | 32bit 浮動小数点  |

|    |                | ・オンチップメモリア                                  | • Yelp                                   | • Para-GCN       |                 | ・重みベクトル:     |

|    |                | クセスの削減                                      |                                          | GraphACT         |                 | 32bit 浮動小数点  |

|    |                | ・オフチップメモリア                                  |                                          |                  |                 |              |

|    |                | クセスの削減                                      |                                          |                  |                 |              |

| 77 | Pipe-          | <ul><li>レイテンシの削減</li></ul>                  | Reddit                                   | • GCN            | • GPU           | N/A          |

|    | GCN[11]        | <ul><li>スループットの向上</li></ul>                 | • OGBN-                                  |                  |                 |              |

|    |                | • GPU 間の通信オーバ                               | Products                                 |                  |                 |              |

|    |                | ーヘッドの削減                                     | • Yelp                                   |                  |                 |              |

|    |                |                                             | • OGBN-                                  |                  |                 |              |

|    | D 1 11 51 11 1 | 44.IW ~ WIDE                                | Papers 100M                              | CDI              | , ara           | 27/4         |

| 78 | Rubik[111]     |                                             | • Collab                                 | • GIN            | • ASIC          | N/A          |

|    |                | <ul><li>オフチップメモリア</li><li>カレス数の判決</li></ul> | • BZR                                    | • Graph-         |                 |              |

|    |                | クセス数の削減                                     | • IMDB                                   | SAGE             |                 |              |

|    |                | ・消費電力削減                                     | • DD                                     |                  |                 |              |

|    |                | • チップ面積削減                                   | • Citeseer                               |                  |                 |              |

| 70 | HP-            | ・フループットのお羊                                  | • Reddit                                 | • GCN            | - CDI I         | NI/A         |

| 79 |                | <ul><li>スループットの改善</li></ul>                 | <ul><li>Flicker</li><li>Reddit</li></ul> |                  | • CPU<br>• FPGA | N/A          |

|    | GNN[112]       |                                             |                                          | • Graph-<br>SAGE | • FPGA          |              |

|    |                |                                             | • Yelp • Amazon-                         | SAGE             |                 |              |

|    |                |                                             | Products                                 |                  |                 |              |

| 80 | GC-            | -<br>・レイテンシの削減                              | • Reddit                                 | • GCN            | • ASIC          | N/A          |

| 80 | Near[113]      |                                             | • Nell                                   | • GIN            | ASIC            | IN/A         |

|    | incar[113]     |                                             | • Amazon                                 | • SAGEConv       |                 |              |

|    |                |                                             | OGBN-                                    | • GAT            |                 |              |

|    |                |                                             | Papers                                   | G/ II            |                 |              |

| 81 | GNNear         | <ul><li>レイテンシの削減</li></ul>                  | • OGBN-                                  | • GCN            | • ASIC          | N/A          |

|    | [33]           | • 消費電力の削減                                   | Proteins                                 | • GIN            |                 |              |

|    | . ,            |                                             | • Reddit                                 | SAGEConv         |                 |              |

|    |                |                                             | • Yelp                                   | • GAT            |                 |              |

|    |                |                                             | Amazon                                   |                  |                 |              |

| 82 | Skeleton       | <ul><li>レイテンシの削減</li></ul>                  | • PPI                                    | • GCN            | • FPGA          | ・特徴ベクトル:     |

|    | -              |                                             | Reddit                                   | Graph-           |                 | 16bit 符号付き整数 |

|    | GCN[114]       |                                             | • Yelp                                   | SAINT            |                 | ・重みベクトル:     |