### **JAIST Repository**

https://dspace.jaist.ac.jp/

| Title        | Advantage of plasma-less deposition: Cat-CVD fabrication of a-Si TFT with current drivability equivalent to poly-Si TFT                                                                                                                                                         |  |  |  |

|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Author(s)    | Matsumura, Hideki; Ohdaira, Keisuke; Nishizaki,<br>Shogo                                                                                                                                                                                                                        |  |  |  |

| Citation     | physica status solidi (c), 7(3-4): 1132-1135                                                                                                                                                                                                                                    |  |  |  |

| Issue Date   | 2010-04                                                                                                                                                                                                                                                                         |  |  |  |

| Туре         | Journal Article                                                                                                                                                                                                                                                                 |  |  |  |

| Text version | author                                                                                                                                                                                                                                                                          |  |  |  |

| URL          | http://hdl.handle.net/10119/9000                                                                                                                                                                                                                                                |  |  |  |

| Rights       | Copyright (C) 2010 WILEY-VCH Verlag GmbH & Co. KGaA, Weinheim. This is the pre-peer reviewed version of the following article: Hideki Matsumura, Keisuke Ohdaira, Shogo Nishizaki, physica status solidi (c), 7(3-4), 2010, 1132-1135. http://dx.doi.org/10.1002/pssc.200982821 |  |  |  |

| Description  |                                                                                                                                                                                                                                                                                 |  |  |  |

44

45

46

47

48

49

50

51

52

53

54

55

56

57

Review copy – not for distribution

(pss-logo will be inserted here by the publisher)

# Advantage of Plasma-Less Deposition; Cat-CVD Fabrication of aSi TFT with Current Drivability Equivalent to Poly-Si TFT

#### Hideki Matsumura, Keisuke Ohdaira, and Shogo Nishizaki

School of Materials Science, Japan Advanced Institute of Science and Technology (JAIST), 1-1 Asahidai, Nomi, Ishikawa 923-1292, Japan

Received ZZZ, revised ZZZ, accepted ZZZ

Published online ZZZ (Dates will be provided by the publisher.)

PACS 85.30.De, 85.30.Tv, 81.15.Gh, 72.15.Cz, 72.20.Fr

This is to study on the advantage of plasma-less deposition in catalytic chemical vapour deposition (Cat-CVD), often called hot-wire CVD. The effects of plasma damage are particularly studied by the performance of amorphous-silicon thin film transistors (a-Si TFTs), since it is strongly affected by the property of an interface between a gate insulating film and an a-Si film. It is found that the plasma damage at the interface affects on off-current of TFT, and that the off-current of Cat-CVD a-Si TFT is much lower than that of a-Si TFT in which all films are prepared by the conventional plasma-enhanced CVD (PECVD). The off-current of Cat-CVD a-Si TFTs is

likely to increase and approach to the same level as the off-current of PECVD a-Si TFT, when Cat-CVD a-Si is exposed to weak plasma. In addition, since the off-current is so low, when the ratio of the channel width (W) to the channel length (L) is adjusted, the on-current can be increased up to the same level as the on-current of poly-crystalline silicon (poly-Si) TFT with keeping the off-current on the same level as that of poly-Si one. That is, it is concluded that a-Si TFT with current drivability equivalent to poly-Si TFT can be produced by using plasma-less Cat-CVD method for preparing films used in TFTs.

Copyright line will be provided by the publisher

**1 Introduction** Among various deposition techniques, catalytic chemical vapor deposition (Cat-CVD) has unique advantages such as simplicity of deposition apparatus. Device-quality amorphous silicon (a-Si) films are obtained with deposition rates as high as 2 nm/s and with high efficiency of gas use [1,2]. The method has also an important advantage as a plasma-less deposition technique. However, this advantage has been forgotten in fabrication of a-Si devices, although the advantage works successfully for the preparation of Si nitride (SiN<sub>x</sub>) coating films on compound semiconductor devices and other devices using feeble materials [3,4].

In fabrication of thin-film devices such as a-Si solar cells and thin-film transistors (TFTs), various films are stacked, and the lower films always suffer from damages during the deposition of the upper films. Here, we particularly investigated the effect of plasma damage in plasmaenhanced CVD (PECVD) onto lower films, and compared it with Cat-CVD. We studied the characteristics of TFT to

know the effect of the upper film deposition, since the stability of the TFT characteristics is sensitive for fabrication process. Bottom-gate a-Si TFTs are fabricated by using Cat-CVD SiN<sub>x</sub>, n<sup>+</sup>-microcrystalline- (µc-) Si or n<sup>+</sup>-a-Si films, and the results are compared with PECVD a-Si TFTs. The effects of a-Si deposition on SiN<sub>x</sub> or Si dioxide (SiO<sub>2</sub>) gate insulators are also investigated by measuring the variation of the TFT characteristics under DC bias stress and current stress. It is found that the on/off current ratio in the transfer characteristics of Cat-CVD a-Si TFTs can be much larger than that of PECVD a-Si TFTs, and reaches to 10<sup>9</sup>. The value is likely to degrade easily after Cat-CVD a-Si TFTs are exposed to weak plasma. The large on/off current ratio appears to come from the deposition without plasma damage in Cat-CVD. It is also confirmed that a-Si TFT with current drivability equivalent to that of poly-Si TFTs can be fabricated by Cat-CVD, by adjusting W/L ratio of the TFTs.

<sup>\*</sup> Corresponding author: e-mail ohdaira@jaist.ac.jp, Phone: +81-761-51-1563, Fax: +81-761-51-1149,

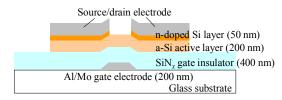

- **2 Fundamentals for Experiment** The cross-sectional view of both PECVD and Cat-CVD a-Si TFTs are shown schematically in Fig. 1. Typical fabrication process of the a-Si TFTs is described as follows;

- 1) Aluminum (Al) and molybdenum (Mo) stacked films 200 nm thick in total or a chromium (Cr) film were formed by sputtering on glass substrates.

- 2) They were patterned by a photolithography to form the gate electrodes and also gate lines.

- 3) 400 nm-thick  $\mathrm{SiN}_{x}$  gate insulator and a 200 nm-thick a-Si active layer were continuously deposited at 320 °C. Here, PECVD a-Si TFTs were fabricated at a company, which is one of the world top-class suppliers of liquid crystal displays (LCDs). The PECVD a-Si TFTs have commercially sufficient performance and stability for the driving of active-matrix LCDs.

- 4)  $n^+$ - $\mu$ c-Si or  $n^+$ -a-Si films were deposited on such a-Si films.

- 5) TFT areas were isolated by an etching process, and source and drain electrodes were formed by the back etching of channel positions.

Cat-CVD a-Si TFTs were fabricated on the same glass substrates as those used for PECVD a-Si TFTs. Defect density of a-Si and SiN<sub>x</sub> films strongly affects the electric properties and stability of a-Si TFTs. Thus, we carefully optimized their deposition conditions. SiN<sub>x</sub> films with the defect density of  $1.3\times10^{17}$  /cm³ and a-Si films with that less than  $10^{16}$  /cm³ were used for Cat-CVD a-Si TFTs in most of cases. The detailed deposition conditions are summarized in Table I.

Apart from the deposition of  $SiN_x$  and a-Si films, other fabrication processes were completely same as those of PECVD a-Si TFTs, in order to compare the performance of Cat-CVD TFTs with PECVD ones. However, in the present paper, just to know the effect of materials of gate insulators in the study on the stability of TFTs, PECVD  $SiN_x$  and  $SiO_2$  films were used as gate insulators. Other results

Figure 1 Schematic view of PECVD and Cat-CVD a-Si TFTs.

**Table 1** Deposition conditions of Cat-CVD films.

|                                                       |      | $SiN_x$ | a-Si | n+-μc-Si |

|-------------------------------------------------------|------|---------|------|----------|

| SiH <sub>4</sub> gas flow rate                        |      | 6       | 50   | 20       |

| NH <sub>3</sub> gas flow rate                         |      | 300     |      |          |

| H <sub>2</sub> gas flow rate                          |      |         | 10   | 200      |

| PH <sub>3</sub> (2%: diluted with He) flow rate       |      |         |      | 10       |

| Catalyzer temperature (T <sub>cat</sub> )             |      | 1750    | 1750 | 1800     |

| Substrate temperature (T <sub>sub</sub> )             |      | 330     | 330  | 330      |

| Gas pressure (Pa)                                     | (Pa) | 15      | 1.1  | 1        |

| Distance between catalyzer and substrate ( $D_{cs}$ ) |      | 14      | 12   | 12       |

shown here are all obtained by the TFT fabricated with the processes described here.

#### 3 Performance of Cat-CVD and PECVD a-Si

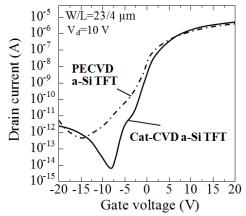

**TFTs** Figure 2 demonstrates the transfer characteristics under a drain voltage ( $V_d$ ) of 10 V in saturation region for both PECVD and Cat-CVD a-Si TFTs with L=4  $\mu$ m and W= 23  $\mu$ m. The field effect mobility  $\mu$  is about 0.6 cm²/Vs and the on/off current ratio is  $10^7$  for a PECVD a-Si TFT and  $10^9$  for a Cat-CVD a-Si TFT. In the figure, it should be noticed that the off-current of Cat-CVD a-Si TFTs is  $10^{-15}$  A, although that of PECVD is  $10^{-13}$  A. The off-current of the Cat-CVD a-Si TFTs is 2 orders of magnitude lower than that of the PECVD ones.

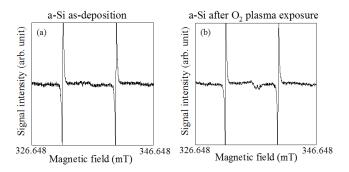

We do not know the exact reason why the off-current of Cat-CVD TFTs becomes lower than that of PECVD ones. One possibility is the influence of the plasma damage on PECVD TFTs. A clear example is demonstrated in Fig. 3. In the figure, The plasma was formed in oxygen gas (O<sub>2</sub>) ambient. The plasma itself was quite weak, and the electric power supplied for generation of plasma was just over the value from which plasma generation started. It is clearly observed that a-Si is damaged by this weak plasma and that a ESR signal due to Si dangling bonds come out.

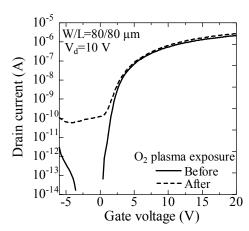

Such plasma damage also degrades the characteristics of a-Si TFTs. Figure 4 shows the transfer characteristics of

Figure 2 Transfer characteristics of PECVD and Cat-CVD TFTs.

**Figure 3** ESR data of a-Si films before (a) and after (b) plasma exposure.

**Figure 4** Transfer characteristics of Cat-CVD a-Si TFT before and after exposure to O<sub>2</sub> plasma.

Cat-CVD a-Si TFTs before and after exposure to the weak plasma in  $O_2$  ambient. TFTs shown schematically in Fig. 1 were simply installed in plasma chamber. Thus, a-Si layer at the position of a back channel might be damaged, and the electron transport through defect states might be added in the off-current. In the conventional fabrication process in PECVD a-Si TFTs, all area of TFTs is covered with a  $SiN_x$  passivation film. This process may cause the increase of the off-current, although we have not checked yet how the off-current behaves when only the final passivation films in PECVD a-Si TFTs are prepared by Cat-CVD.

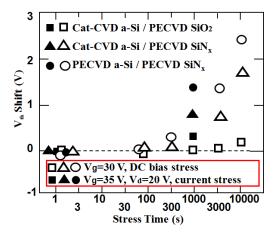

**4 Instability of a-Si TFTs** When a-Si films are deposited on gate insulator, the plasma may make damage on gate insulating films. When the gate insulator is damaged, the trap states are formed there, and they may cause the instability such as threshold voltage ( $V_{th}$ ) shift in a-Si TFTs due to charge trapping.

Here, V<sub>th</sub> shift after DC-gate bias stress and current stress are observed for 3 types of bottom gate a-Si TFTs. For only this experiment, TFTs were specially prepared apart from the fabrication conditions described in chapters

**Figure 5** V<sub>th</sub> shift of a-Si TFTs as a function of stress time.

2 and 3. Type a) has a structure of Cat-CVD a-Si/PECVD  $SiO_2$  gate insulator/gate-metal/glass, type b) has Cat-CVD a-Si/PECVD  $SiN_x$  gate insulator/gate-metal/glass, and type c) has PECVD a-Si/PECVD  $SiN_x$  gate insulator/gate-metal/glass. Two types of stresses were also applied on such 3 types of a-Si TFTs. One was applying gate voltage (Vg) of 30 V but no drain voltage (Vd), and second was applying both  $V_g$ =35 V and  $V_d$ =20 V. The first one is called DC bias stress and the second one is current stress.

Figure 5 shows  $V_{th}$  shift for 3 types of a-Si TFTs as a function of stress time. It is firstly found that  $V_{th}$  shift is negligibly small when a PECVD  $SiO_2$  film is used as a gate insulator a below Cat-CVD a-Si channel layer, even when the DC stress was applied for  $10^4$  s and the current stress for  $10^3$  s. When a Cat-CVD a-Si layer is deposited on PECVD  $SiN_x$  gate insulator, slight shift of  $V_{th}$  can be detected. However, the  $V_{th}$  shift became more apparent, when a PECVD a-Si layer was deposited on a PECVD  $SiN_x$  gate insulating layer.

The difference between types b) and c) TFTs can be understandable, because plasma damage is introduced inside the PECVD  $SiN_x$  gate insulating layer during a-Si deposition. Newly generated trap states in the gate insulator will cause the shift of  $V_{th}$ . PECVD  $SiN_x$  films probably have certain trap states before a-Si films are deposited and the effect of plasma-less deposition of Cat-CVD may be masked. Even so, the  $V_{th}$  shift of type b) TFT appears smaller than that of type c) TFTs.

The reason why TFT with  $SiO_2$  gate insulator is stable is not clear at the moment. We have not measured the initial defect density of PECVD  $SiO_2$  and  $SiN_x$  films. Thus, we cannot say exact mechanism for the difference of stability. When a-Si films are deposited, the layer below it may suffer from not only plasma damage but also hydrogen attack. It is known that high density hydrogen can etch a substrate. If PECVD  $SiN_x$  films are not perfect, it would be suffer from both plasma damage and hydrogen etching to make rough interface. However, perfect  $SiO_2$  is very tough for such hydrogen attack. This may be one possible reason to explain the results of Fig. 5. Anyway, it is suggested that Cat-CVD a-Si TFTs can be very stable if proper gate insulator is provided.

## **5. High Current Drivability of Cat-CVD a-Si TFTs** As mentioned above, Cat-CVD a-Si TFT can be used as a new type a-Si TFTs with extremely high stability.

used as a new type a-Si TFTs with extremely high stability. Thus, if the high current drivability can be added to this, a-Si TFT equivalent to poly-Si TFTs can be produced by using Cat-CVD technology. The remarkably low off-current in all Cat-CVD a-Si TFTs enables to realize TFTs with high on-current, equivalent to poly-Si TFTs by simply increasing the W/L ratio keeping the low off-current still low enough.

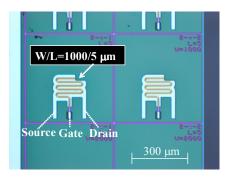

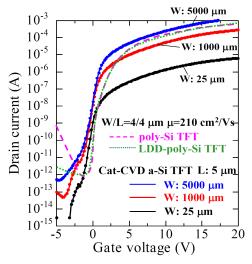

Figure 6 shows a-Si TFTs with comb-like source and drain electrodes, by which large W/L can be realized without enlarging TFT area. Figure 7 shows the transfer characteristics of the Cat-CVD a-Si TFTs with comb-like elec-

trodes having W of 25, 1000 and 5000  $\mu m$  and L of 5  $\mu m$  for  $V_d \!\!=\!\! 8$  V. In the figure, typical transfer characteristics of a lightly-doped-drain (LDD) poly-Si TFT with the mobility  $\mu$  of 210 cm²/Vs are also demonstrated for comparison. Even if the W of the Cat-CVD a-Si TFTs increases up to 1000 or 5000  $\mu m$ , the off-current is still smaller than that of the poly-Si TFTs. On the other hand, it is shown that the on-current of Cat-CVD a-Si TFTs is equivalent to the poly-Si TFTs.

The time used for electron transport between source and drain electrodes is expressed by  $(4/3)L^2/(\mu V_d)$  when the space charge has to be taken into account for high resistivity materials such as a-Si. The transit time through the channel is about 0.1  $\mu s$  for L=5  $\mu m$  and  $\mu$  is only 0.3 cm²/Vs. The value is enough for the pixel control of organic electro-luminescence displays or other circuit controllers. This appears suggestive for feasibility of Cat-CVD a-Si TFTs, which is fabricated with plasma-less deposition.

Figure 6 a-Si TFTs with comb-like source and drain electrodes.

**Figure 7** Transfer characteristics of the Cat-CVD a-Si TFTs with comb-like electrodes.

- **6. Conclusion** From the above results, the follows are concluded:

- 1) Cat-CVD a-Si TFTs with current drivability equivalent to that of poly-Si TFTs can be prepared by in-

- creasing W/L, since the off-current of Cat-CVD a-Si TFTs is almost 2 orders of magnitude smaller than that of PECVD a-Si TFTs.

- 2) Low off-current appeared in Cat-CVD a-Si TFTs is probably due to the low damage process of Cat-CVD.

- 3) According to preliminary experiment using PECVD  $SiO_2$  and  $SiN_x$  films as gate insulators, it is found that best stability appears seen when a Cat-CVD a-Si active channel layer is deposited on  $SiO_2$  gate insulator.

- 4) If proper gate insulator is provided to Cat-CVD a-Si TFTs, highly stable a-Si TFT will be realized, which has excellent current drivability just like poly-Si TFTs.

#### References

- [1] H. Matsumura, H. Umemoto, and A. Masuda, J. Non-Cryst. Solids 338–340, 19 (2004).

- [2] N. Honda, A. Masuda, and H. Matsumura: J. Non-Cryst. Solids 266-269, 100 (2000).

- [3] M. Higashiwaki, T. Matsui, and T. Mimura, IEEE Trans. Electron Device Lett. 27, 16 (2006).

- [4] Y. Ogawa, K. Ohdaira, T. Oyaidu, and H. Matsumura, Thin Solid Films **516**, 611 (2008).